# 2018 ECTC Panel Session IC/Package Co-Design of Heterogeneous Integrated Systems

## Multi-Physics and Multi-Scale Modeling

Xuejun Fan

Lamar University

Beaumont, Texas 77710

xueiun.fan@lamar.edu; 409-880-7792

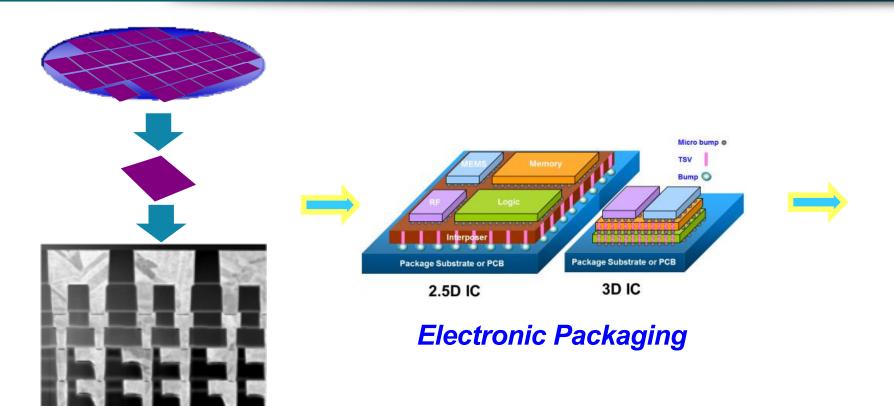

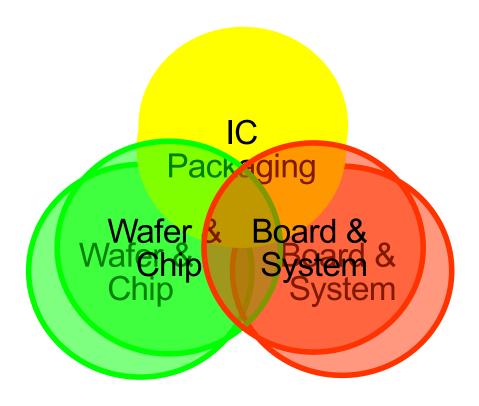

### Wafer, Package, Board and System Levels

**Board and System**

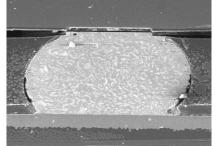

Wafer Fabrication & Backend Process

LAMAR UNIVERSITY

MEMBER THE TEXAS STATE UNIVERSITY SYSTEM

ECTC 2018 – San Diego, CA May 29 – June 1, 2019

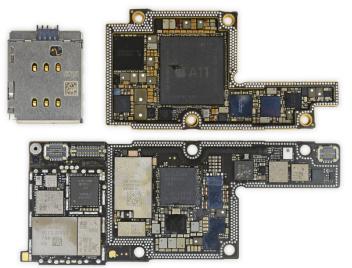

#### Wafer, Package, Board & System Levels

Design of a package must consider the interactions among wafer, package, and board (e.g. CPI – chip-package-interaction).

LAMAR UNIVERSITY

MEMBER THE TEXAS STATE UNIVERSITY SYSTEM

ECTC 2018 – San Diego, CA

May 29 – June 1, 2019

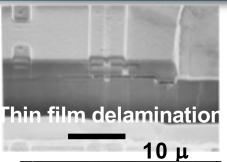

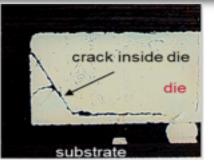

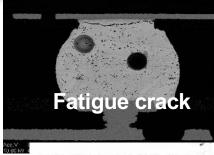

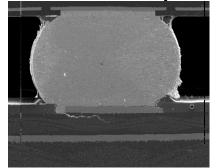

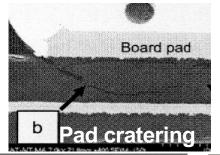

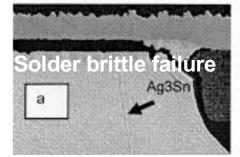

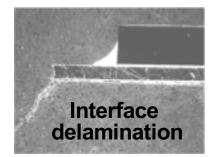

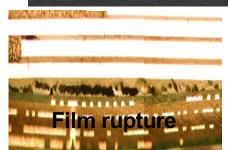

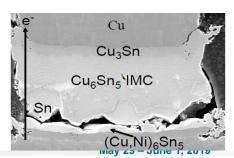

## Typical Failures under Various Stresses

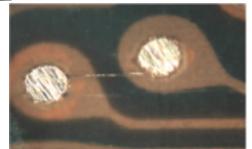

Moisture load

Electrical current

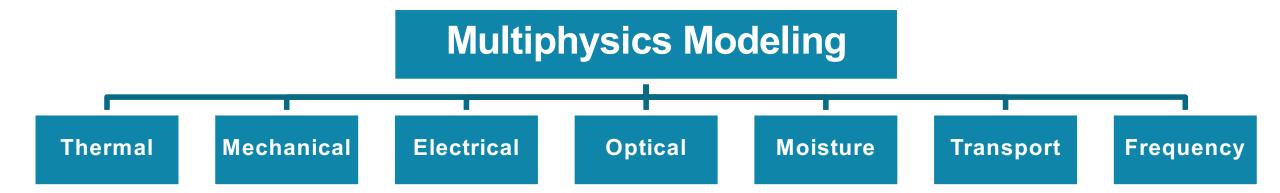

#### **Need for Multiphysics Modeling**

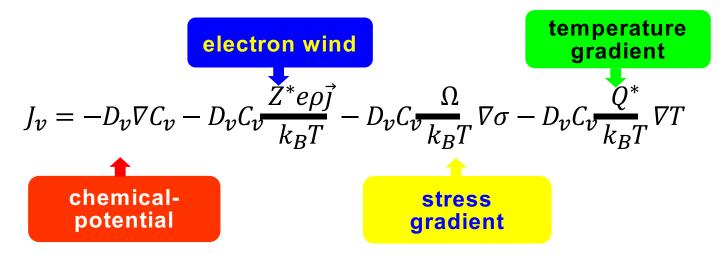

#### An example – electromigration modeling

ECTC 2018 – San Diego, CA

May 29 – June 1, 2019

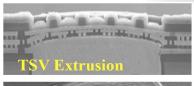

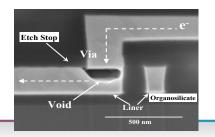

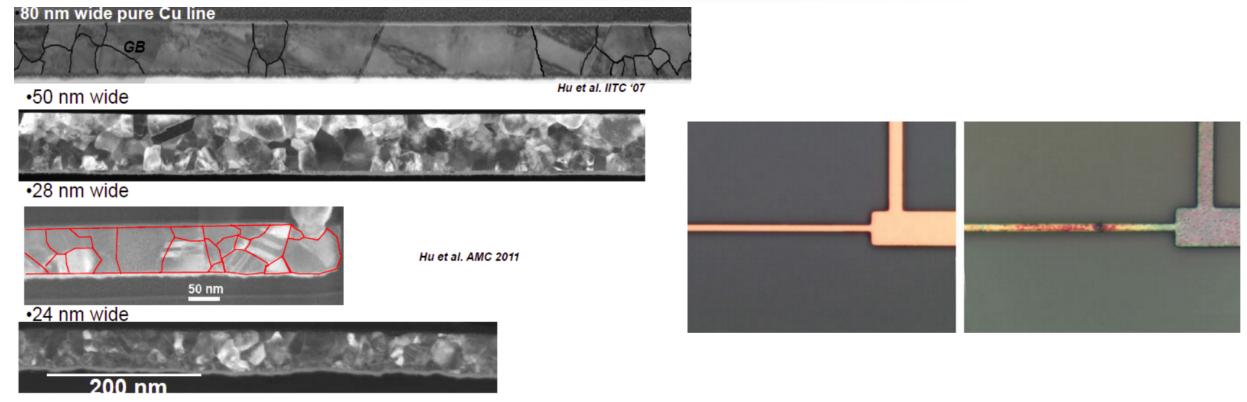

#### **Need for Nano-Scale Modeling**

- Today's 14-nanometer-node processors contain more than 10 km in the same area.

- Today's solution is to deposit copper interconnects within trenches lined with 2-nanometer-thick walls of tantalum nitride.

- At 0.3 nm, graphene might be an option.

CK Hu, Impact of impurities, liner, Co cap and short length on electromigration in Cu damascene lines, 2014 Stress Workshop, Austin. SJ Yoon, Improved electromigration-resistance of Cu interconnects by graphene-based capping layer. 2015 VLSI Technology (VLSI Technology)

LAMAR UNIVERSITY

MEMBER THE TEXAS STATE UNIVERSITY SYSTEM

ECTC 2018 – San Diego, CA

May 29 – June 1, 2019

First principles simulation

Molecular dynamics simulation

Finite element simulation

Z Cui, X Chen, X Fan, GQ Zhang, Interfacial Properties of Cu/SiO2 using a Multiscale Modelling Approach in Electronic Packages, EuroSimE 2018.

ECTC 2018 – San Diego, CA May 29 – June 1, 2019

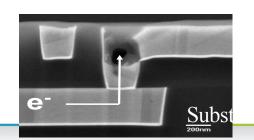

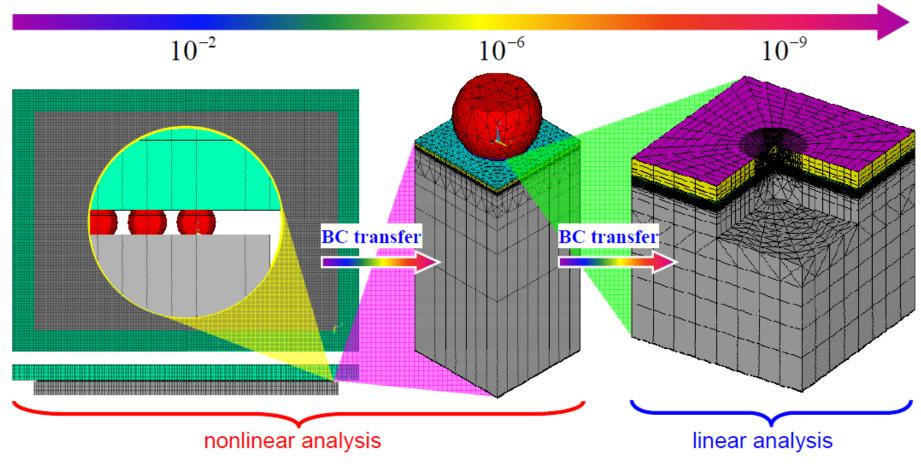

#### State of the Art: Multilevel Submodeling Technique

- ☐ Multilevel models are chained to obtain the driving force for delamination.

- ☐ Thousands of lines in ANSYS APDL codes have been written for the model.

- ☐ Typical model has one million DOF and takes a few hours to solve.

XH Liu, TM Shaw, G Bonilla - Advanced Metallization Conference, 2010 - sematech.org

ECTC 2018 – San Diego, CA May 29 – June 1, 2019

#### **Summary**

#### The state of the art

- Multiphysics modeling software available.

- Open source code for materials modeling at each scale available.

#### Key challenges that need to be overcome to enable

- Fundamental theory on constitutive relationship.

- Characterization of material properties at different scales.

- Bridging among different scales.

#### What needs to happen to overcome these challenges?

- Develop fundamental constitutive theory for material behavior.

- Develop theory and implementation for multiscale modeling.

- Develop micro-/nano-scale material characterization techniques.

May 29 - June 1, 2019

ECTC 2018 – San Diego, CA