## LED Packaging Challenges ECTC 2012 San Diego, CA

#### **Jeff Perkins**

#### perkins@yole.fr

75 cours Emile Zola, 69100 Lyon-Villeurbanne, France Tel: +33 472 83 01 80 - Fax: +33 472 83 01 83 Web: http://www.yole.fr

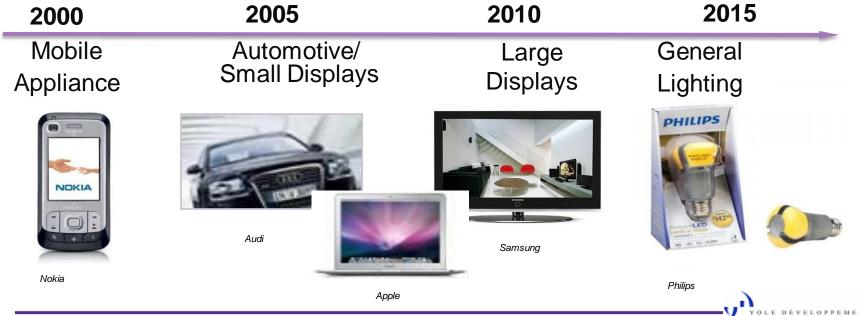

#### **Recent LED History**

- The HB LED market was enabled in the mid 90's with blue LEDs.

- Cell phone provided the first "killer app" (screen and keypad)

- As technology improved, LED addressed larger displays: phones → netbooks → notebooks → desktop monitor → large TV

- And now the push is on for General Lighting

© 2011 2

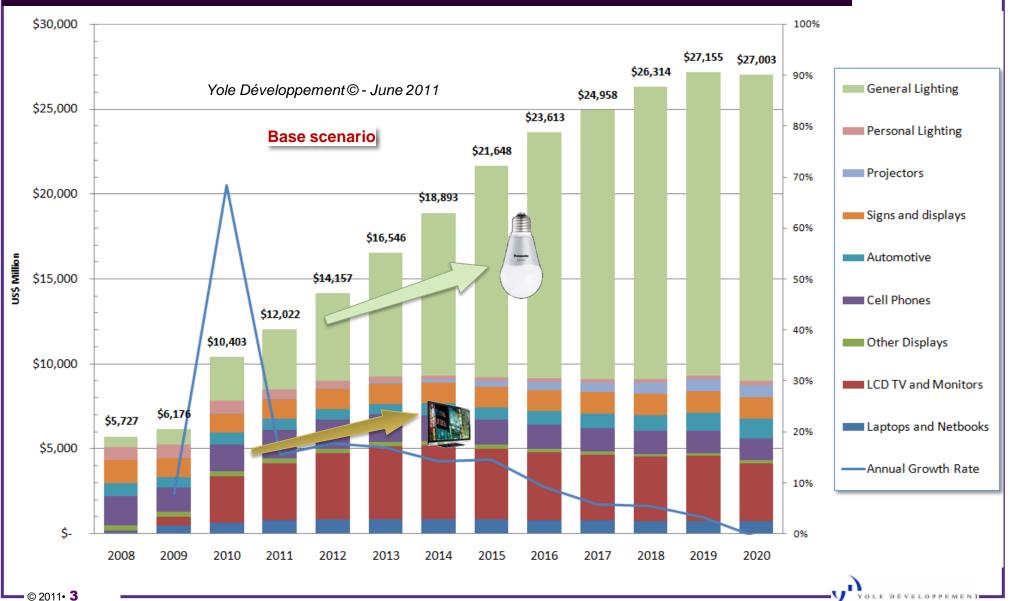

#### **Revenue Forecast** packaged LED die, by application

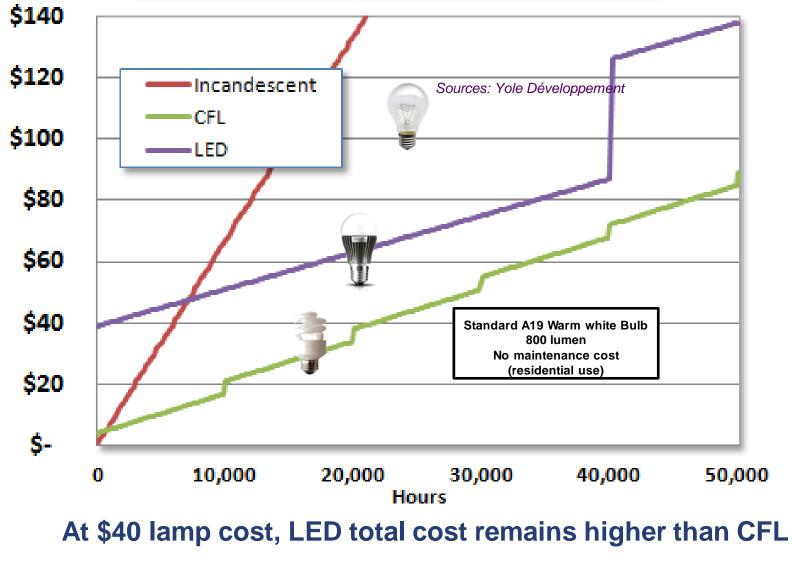

## **Focus is on Cost**

\*All sources: ~ 800 lumens, warm White, tier 1 brand only

## Total Cost of Light =

## **Upfront Cost**

+

# Energy Cost

#### **Total Cost** \$40 LED, \$3 CFL, \$1 Thomas Edison

#### **General Lighting** people focus on purchase price!

## **Upfront Cost**

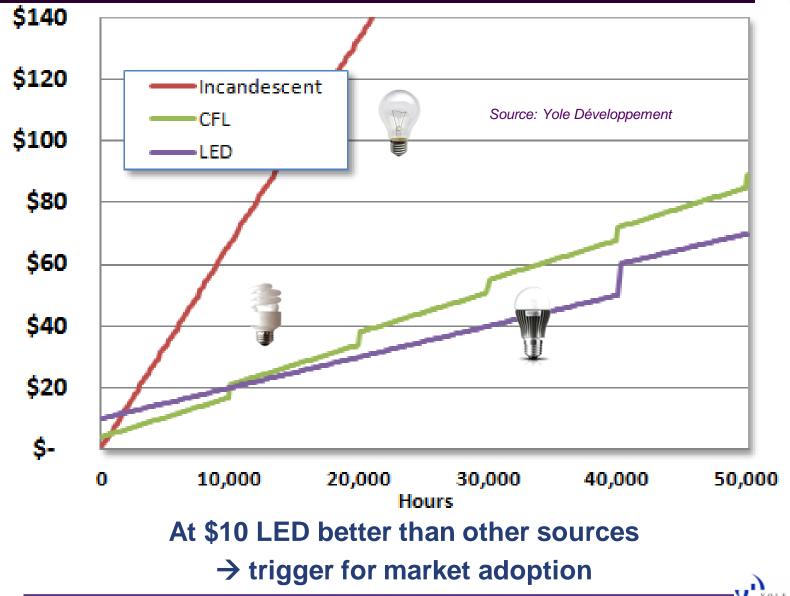

\$10 ?

\*All sources: ~ 800 lumens, warm White, tier 1 brand only

#### Total Cost LED at \$10

**-** © 2011• **8**

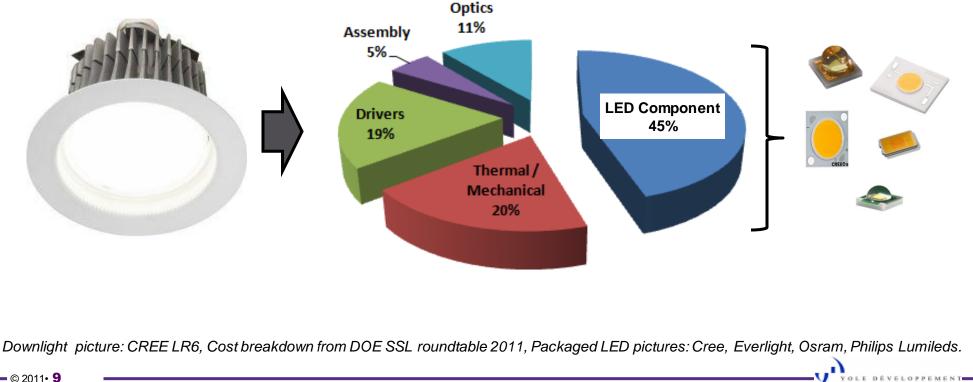

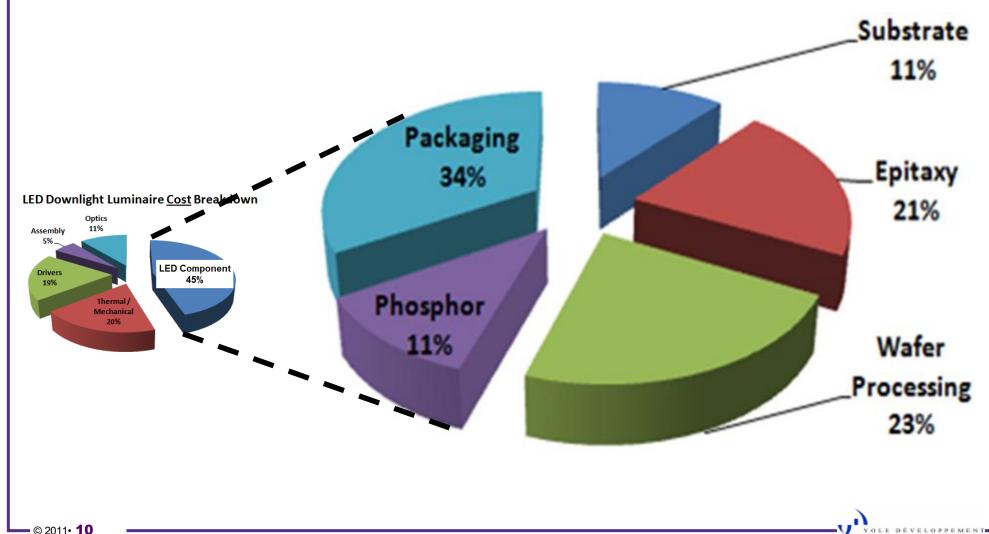

#### **Luminaire Cost Structure**

#### LED is only one contributor but represents the single largest opportunity for cost reduction:

LED Downlight Luminaire <u>Cost</u> Breakdown

#### Driving Down Cost typical cost structure, PACKAGED DIE

#### Packaging represents up to 40% of the packaged LED cost

#### **Key Components of a Packaged LED**

Note: some elements described here can be optional or redundant depending on the exact design choices made by the manufacturer.

#### High-Power LED Packages wide variety of solutions

Single Large Die (1 die, typical dimension: 0.5 to 1.5 mm)

Osram

Multiple Large Dice

(3 to 25 dice, typical dimension: 0.5 to 1.5 mm each)

Osram

Osran

#### Small/medium dice Array

(20 to 100 dice, typical dimension: 250 to 500 um each)

Edison Opto

Single or Multi "Jumbo Die"

1 to 6 dice, typical dimension 2 to 5 mm each)

Luminus Device

Copyrights © Yole Développement SA. All rights reserved.

© 2011• **12**

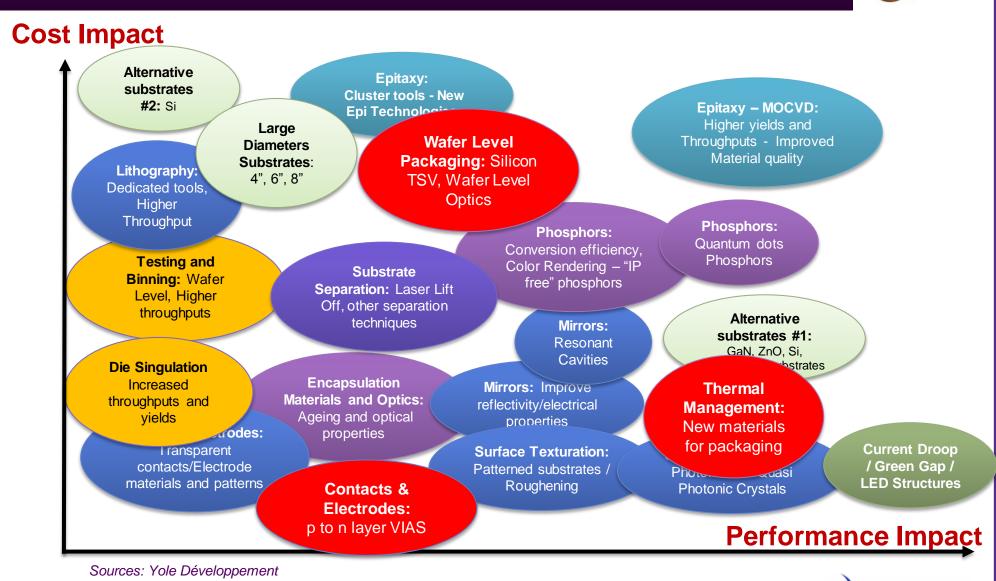

#### Key Technologies & Research Areas addressing LED cost of ownership

#### **Thermal Management**

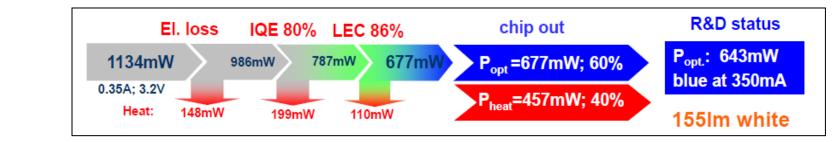

R&D status of Electrical and optical power flow in packaged LED (source: Osram)

- For a 1W LED, 40% of the input power turns into heat.

- <u>Most importantly</u> for the packaging task... LED heat is <u>not</u> radiated and has to be removed by conduction:

| Source       | Radiation<br>heat loss | Convection<br>heat loss | Conduction<br>heat loss |

|--------------|------------------------|-------------------------|-------------------------|

| Incandescent | 90%                    | 5%                      | 5%                      |

| Fluorescent  | 40%                    | 40%                     | 20%                     |

| LED          | 10%                    | 10%                     | >80%                    |

IR imaging of the temperature distribution of LED based, Incandescent and CFL Bulb (Source: Tyrone Turner/National Geographic Society / Corbis)

**-** © 2011• **14**

Copyrights © Yole Développement SA. All rights reserved.

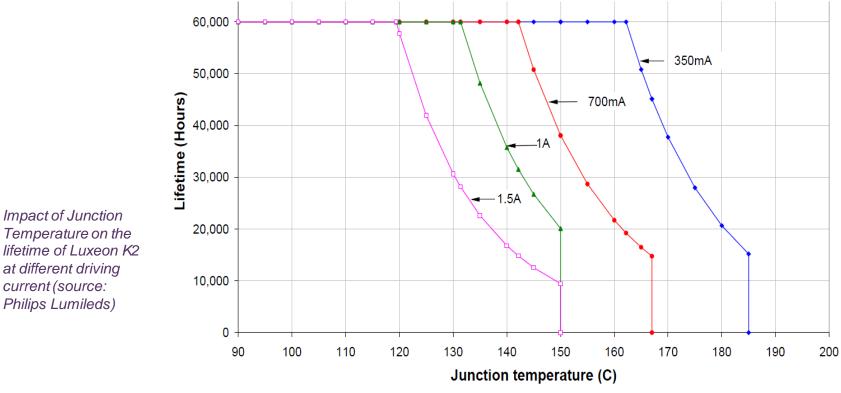

### **Thermal Management**

- Heat has a significant impact on LED performance and reliability

- Lifetime: Lumen maintenance, catastrophic failure.

- Energy efficiency: Lumen/Watt, bias voltage.

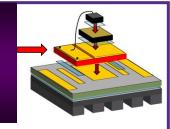

#### <u>Thermal management is a critical aspect of LED performance and reliability.</u> <u>An efficient conduction path needs to be built in the package to get heat out</u>

#### Thermal Management material options

DÉVELOPPEMEN

|                                     | Thermal<br>Conductivity<br>(W/m.K)     | CTE<br>(ppm/°C)                     | Cost           | comments                                                                                                       |

|-------------------------------------|----------------------------------------|-------------------------------------|----------------|----------------------------------------------------------------------------------------------------------------|

| Lead Frame / Metal<br>Slug          | High<br>(Al:150– 230 / Cu:<br>400)     | Low to Medium<br>(Al: 2.7 / Cu:8.9) | Medium         |                                                                                                                |

| Printed Circuit<br>Board (FR-4)     | Low<br>(0.36)                          | High<br>(13 – 17)                   | Low            | <ul> <li>Available for large<br/>panel size</li> </ul>                                                         |

| Metal Core Printed<br>Circuit Board | Low through<br>dielectric<br>(1 - 2.2) | High<br>(17 - 23)                   | Medium to high | <ul> <li>Available for large<br/>panel size</li> <li>Operating<br/>temperature limited to<br/>140°C</li> </ul> |

| CERAMIC                             | Medium to high<br>(20 – 230)           | Medium to high<br>(4.9 – 8)         | Medium to high | •Small panel sizes<br>•Very high operating<br>temperatures<br>•Easily handles high<br>power                    |

| Silicon                             | High (150)                             | Low (3.2)                           | Medium to High | <ul> <li>High potential with<br/>TSV technology and<br/>wafer Level Packaging</li> </ul>                       |

|                                     |                                        |                                     |                |                                                                                                                |

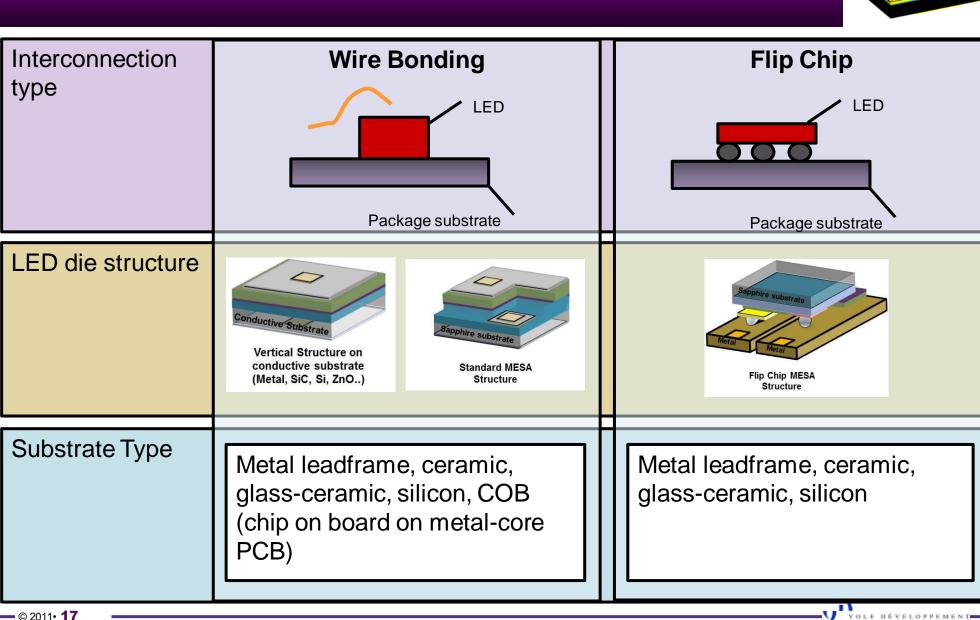

#### Interconnects

#### Interconnects

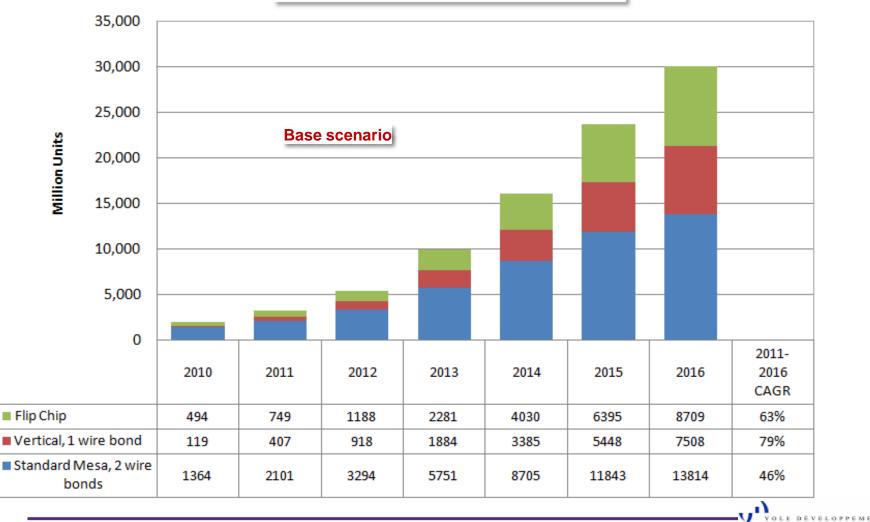

#### Interconnection of large size LEDs

by interconnection types (Mu)

© 2011• **18**

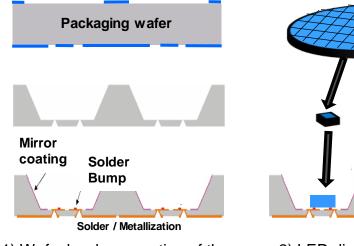

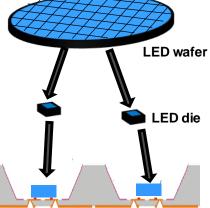

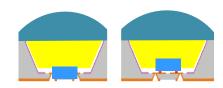

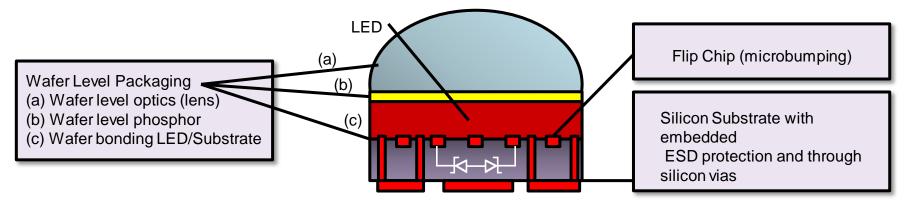

### Wafer Level Packaging

- Packaging of an LED at wafer level, rather than assembling the package of each individual unit after wafer dicing

- LED Wafer Level Packaging leverages experience and technology platforms developed for MEMS, CMOS image sensors and Wafer Level Optics.

1) Wafer level preparation of the bare package (cavity etching,  $SiO_2$  insulation layer, via / bump interconnects, mirrors...)

2) LED die separation + pick and place positioning on the package wafer. *in this example, the LED chips are singulated* <u>before</u> being positioned onto the package wafer (="Chip to Wafer" packaging)

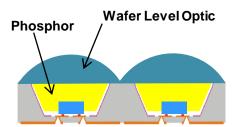

3) Wafer level interconnect, phosphor deposition, encapsulation, optic.

4) LED package separation.

Overview of Chip to Wafer LED WLP process (Yole, Hymite)

Wafer Level Packaging

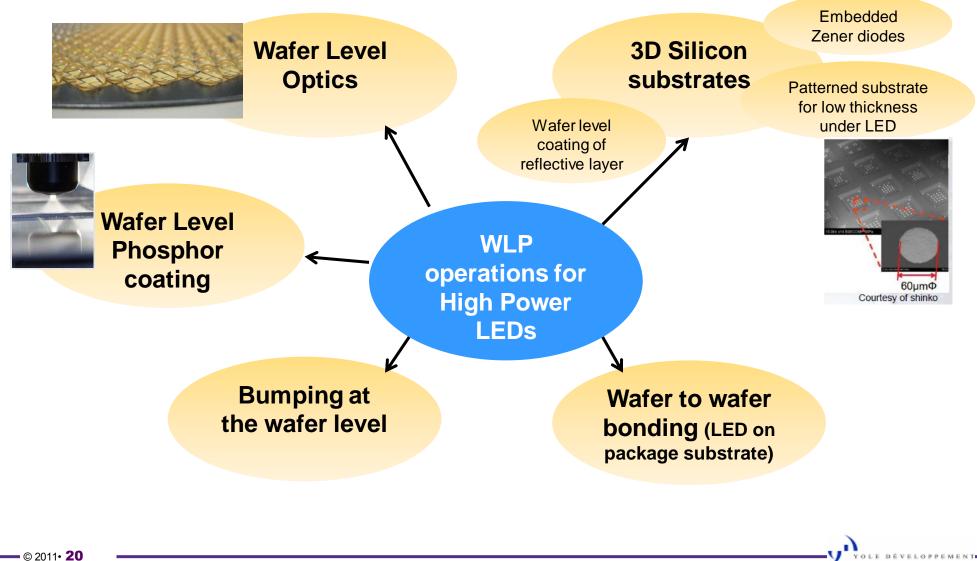

#### **WLP for High Power LEDs**

Copyrights © Yole Développement SA. All rights reserved.

#### WLP Long Term Vision: Wafer to Wafer packaging?

- A number of players have roadmaps to a "fully integrated 3D WLP LED package"

- Benefits:

- A record small size package in all 3 dimensions

- Excellent thermal properties (thin substrate, copper filled vias) and reliability (low CTE, early ESD protection in the flow)

- Low cost: as LED wafers migrate to 6-inch and possibly 8-inch wafers, the LED industry will access wafer capacity freed by the semiconductor industry (still moving to 12 inch). Also the substrate size shrinks from 10-15mm<sup>2</sup> today for a 1mm<sup>2</sup> LED die down to 1mm<sup>2</sup>-2mm<sup>2</sup> LED and package size, thus considerably lowering material costs.

#### Critical technologies to develop are

- Silicon <u>substrates with through silicon vias and embedded zener diodes</u>: as of 2011, only LG Innotek produces such substrates

- LED wafer to substrate wafer bonding

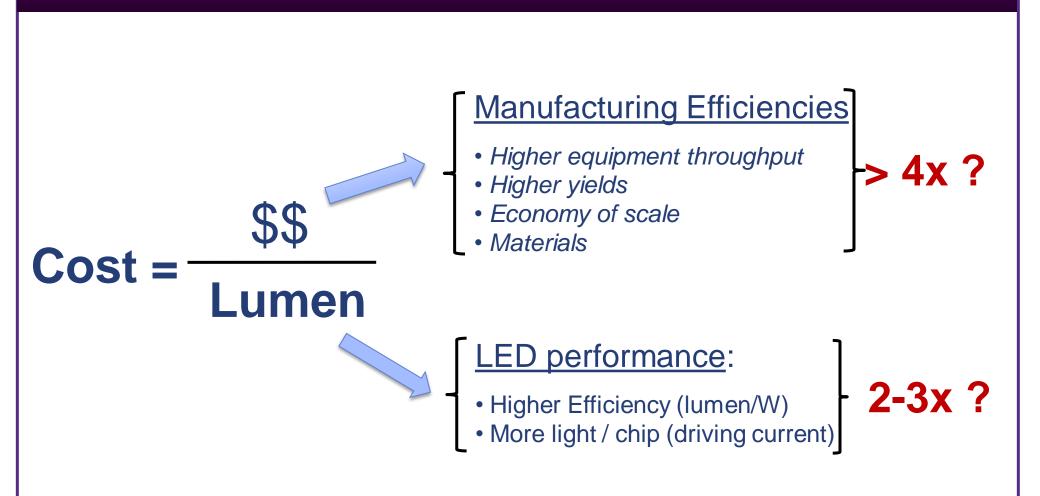

#### **The Path to Cost Reduction**

#### Conclusion

- A 10x cost improvement of packaged LED is required to enable massive adoption of LEDs in general lighting.

- LED can only rely on performance improvement and manufacturing cost reduction to reach the cost targets.

- Packaging represents 40%++ of the cost of a packaged LED and therefore will have to contribute significantly to the cost reduction effort.

- Over time the industry will adopt methods coming from the IC industry such as Wafer Level Packaging.

#### US DOE SSL Roadmap

|                      | Metric                                  | 2010 Status | 2015 Target                   |

|----------------------|-----------------------------------------|-------------|-------------------------------|

| Testing              | Throughput (UPH)                        | /           | 2x Increase                   |

|                      | Cost of Ownership                       | /           | 2-3x reduction every 5 years. |

|                      | \$/Units per hour                       | /           | /                             |

| Phosphor Materials   | Batch size (kg)                         | 1 to 5      | >20                           |

|                      | Cost (\$/kg)                            |             | 50% reduction every 2-3 years |

|                      | Material Usage Efficiency               | 50%         | 90%                           |

|                      | PSD Range Uniformity                    | 30          | 10                            |

|                      | Duv control                             | 0.012       | <0.002                        |

| Phosphor Deposition  | Thickness Uniformity (1 sigma)%         | 5           | 2                             |

|                      | Cost (\$/klm)                           | /           | 50% reduction every 2-3 years |

|                      | Device to Device Reproducibility (SDCM) | 4           | 2                             |

| Packaged LED Metrics | LED Efficacy (2580-3710K, 80-90 CRI)    | 88 lm/W     | 184 /lm/W                     |

|                      | LED Price (2580-3710K; 35 A/cm2)        | 25 \$/klm   | 3 \$/klm                      |

|                      | LED Efficacy (4746-7040K, 70-80 CRI)    | 134 lm/W    | 215 lm/W                      |

|                      | LED Price (4746-7040K; 35 A/cm2)        | 13 \$/klm   | 2 \$/klm                      |

Source: "Solid State Lighting LED Manufacturing Roundtable Summary" – March 2011 (www1.eere.energy.gov/buildings/ssl/)

It's not who you know today. It's who you need to know tomorrow!

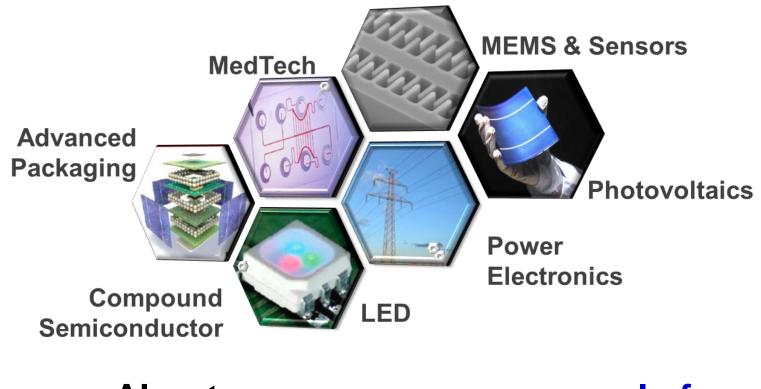

About these markets: www.i-micronews.com

About our company: <u>www.yole.fr</u>