### 2014 CPMT Seminar

Latest Advances in Organic Interposers

# **3D-ICs: Advances in the Industry**

Suresh Ramalingam

Advanced Packaging, Xilinx 2100 Logic Drive, San Jose, 95124 **XILINX**.

IEEE 64th ECTC – Orlando, FL, USA

May 27-30, 2014

### Outline

- > 3D IC Background

- > 3D IC Technology Development

- Summary

- > Acknowledgements

Stacked Silicon Interconnect Technology refers to Xilinx 3D solutions

**XILINX**

# **3D IC Background**

**XILINX**.

IEEE 64th ECTC – Orlando, FL, USA

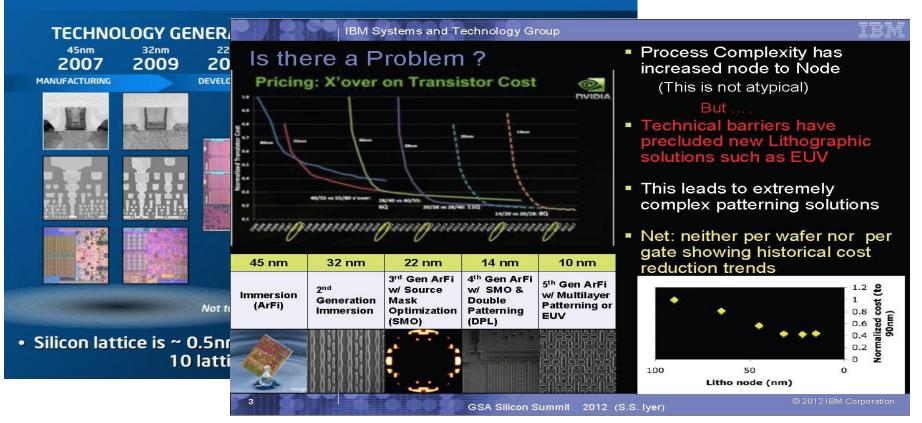

# **Technical Challenges & Costs Are Growing**

### Our visibility always ~10 yrs - need broad exploration

> Process Technology Path Below 10nm is unclear

Cost Reduction Slowing from Complexity / Investment Increases

Cost Per Wafer & Cost Per Gate Deviating from Historical Reduction

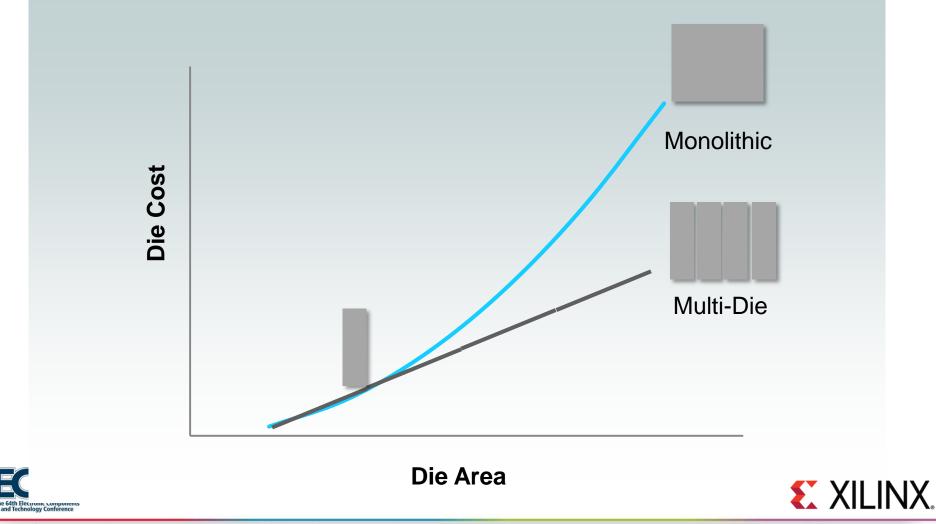

# **3DIC Extends Moore's Law** *Cost Comparison: Monolithic vs. Multi-Die*

### "Moore's Law is Really About Economics" – Gordon Moore

# **Design Rule Comparison**

| Design Rules for Die to<br>Die interconnection                   | MCM<br>(Substrate) | MCM with<br>Silicon Bridge     | Silicon<br>Interposer<br>(65 nm BEOL) | WLFO /<br>Organic<br>Interposer |

|------------------------------------------------------------------|--------------------|--------------------------------|---------------------------------------|---------------------------------|

| Minimum Bump pitch (um)                                          | 150 (C4)           | 150 (C4)<br>40 (u-bump) bridge | < 40 (u-bump)                         | 40 um RDL pad<br>pitch          |

| Via size / pad size (um)                                         | 60 / 90            | 0.4 / 0.7                      | 0.4 / 0.7                             | 10/30                           |

| Minimum Line & Space (um)                                        | 15 / 15            | 0.4 / 0.4                      | 0.4 / 0.4                             | 3/3                             |

| Metal thickness (um)                                             | 10                 | 1                              | 1                                     | 2-5                             |

| Dielectric thickness (um)                                        | 30                 | 1                              | 1                                     | < 5                             |

| # of die-to-die connections per<br>layer + GND shield layer (2L) | 100's              | 10,000's                       | 10,000's                              | 1000's                          |

| Minimum die to die spacing (um)                                  | 4000               | Bridge ~ 2500                  | 150                                   | < 250                           |

| # of High density layers feasible                                | Not a limitation   | Not a limitation               | Not a limitation                      | 1-3L layers                     |

| Die Sizes for assembly and # of assemblies                       | Not a concern      | Size & # limitation?           | Not a concern                         | Size limitation?                |

ECCICe14 The 64th Electronic Components and Technology Conference Xilinx pursuing Silicon Interposer for design rule density, BW and lower power – e.g. die partition

IEEE 64<sup>th</sup> ECTC – Orlando, FL, USA

**E** XILINX

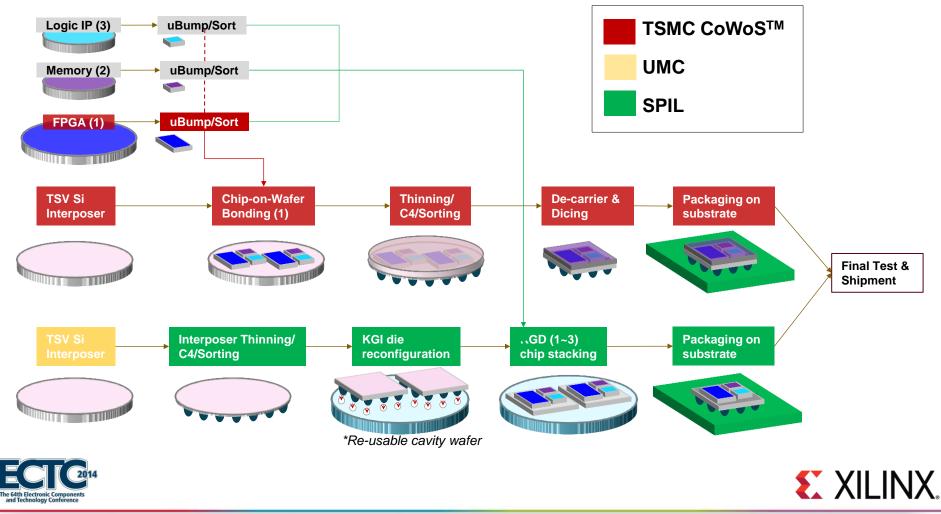

# **Supply Chain**

- > TSMC CoWoS in production

- > Readying UMC/SPIL as additional source. Completed technology qualification

## Xilinx 28nm 3DIC – Huge Leap in Innovation

### Earth

Area: ~500 Million km<sup>2</sup> Population: ~6.8 Billion People Oceans: 5

### Interposer Area: ~775 mm<sup>2</sup> Population: ~6.8 Billion Transistors Chips: 5

Virtex-7 2000T

# 136 Patents Awarded Worldwide 226 Pending Applications Worldwide

IEEE 64th ECTC – Orlando, FL, USA

May 27 – 30, 2014 8

# **3D IC Technology Development**

IEEE 64th ECTC – Orlando, FL, USA

**Suresh Ramalingam**

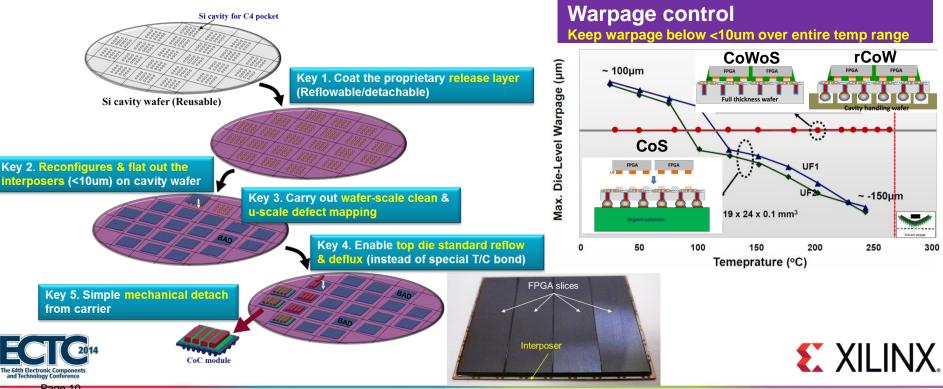

# **Critical Challenge: Warpage Control**

### CoWoS Technology

Top dies are attached to full-thickness interposer wafers thus getting around the thin interposer warpage and poor micro-bump joining problem

### Reconfigurable CoW (rCoW) Technology

- Xilinx patent issued worldwide (US/TWN/CN/EU/IND/JPN/KR)

- Release layer approach that withstands reflow & maintains low warpage

IEEE 64<sup>th</sup> ECTC – Orlando, FL, USA

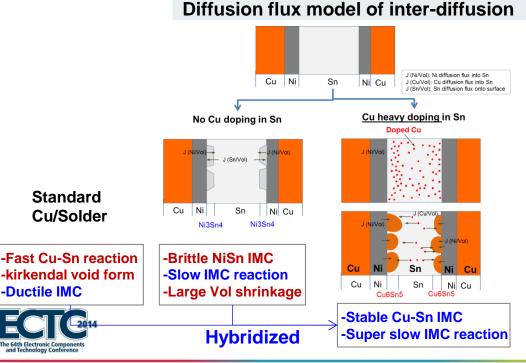

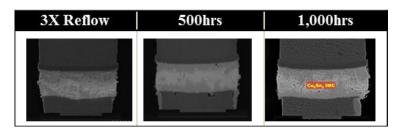

# **HTS Aging Reliability Issue**

### > Voiding or crack in micro-joint during long term stress (HTS in particular)

- Due to limited Sn source and its dual consumption rate from top and bottom pad.

### > Resolution : Heavy Cu doping into LF solder cap (with Ni barrier layer)

- Take advantages of ductile IMC (Cu-Sn) and slower IMC reaction (Ni with Cu-Sn IMC)

- Passed 3X reflow + 150°C aging condition for > 1000 hrs

- Xilinx X-4281 patent pending

#### HTS aging performance

\*Reference images (from no-doping u-bump)

IEEE 64th ECTC – Orlando, FL, USA

# **3D IC Technology Landscape**

|                 | Chip level                                                                        | Device level                                                        | W2W C2W level                                                |  |  |

|-----------------|-----------------------------------------------------------------------------------|---------------------------------------------------------------------|--------------------------------------------------------------|--|--|

| Players         | Samsung DRAM / Hynix NAND &<br>DRAM / IBM / Micron / Elpida /<br>Qualcomm / Nokia | Samsung Vertical-Gate NAND/<br>Besang / Monolithic 3D IC / Stanford | SONY (Stacked CIS) / Tezzaron /<br>Ziptronix/ MIT Lincon Lab |  |  |

| TSV size        | 5~10um                                                                            | 0.5~2um contact through oxide                                       | 2~5um in diameter                                            |  |  |

| TSV pitch       | 30~50um                                                                           | 1~4um (not limited)                                                 | 5~10um                                                       |  |  |

| TSV count       | 1k~5k                                                                             | Not limited                                                         | Not limited                                                  |  |  |

| Key<br>features | <complex-block></complex-block>                                                   | <figure></figure>                                                   | <complex-block></complex-block>                              |  |  |

IEEE 64th ECTC – Orlando, FL, USA

The 64th Electronic Component

IEEE 64th ECTC - Orlando, FL, USA

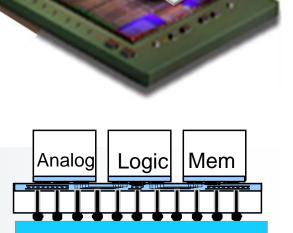

Economic and technology forces are aligned to enable 2.5D/3D stacking

TSV and 3D stacking already deployed in Smartphones, High end FPGAs & Servers

The "end game" will see three distinct technologies: Logic, Memory, Analog

Suresh Ramalingam

# Acknowledgements

### Xilinx

- R&D, NPI & Operation Teams

### Partners

- TSMC R&D and Production Teams for FPGA, CoWoS

- UMC for Interposer

- SPIL R&D for MEOL and Advanced Packaging

- Fujitsu Interconnect Technology for High Speed Substrates