Disruptive Developments for Advanced Die Attach to Tackle the Challenges of Heterogeneous Integration

Bes

Hugo Pristauz & Andreas Mayr, Besi Austria presented by: Stefan Behler, Besi Switzerland

ECTC 2018 / San Diego

**Current Integration Architectures**

Besi

**Future Integration Architectures**

**Demand for High Capabilities**

**Disruptive Developments**

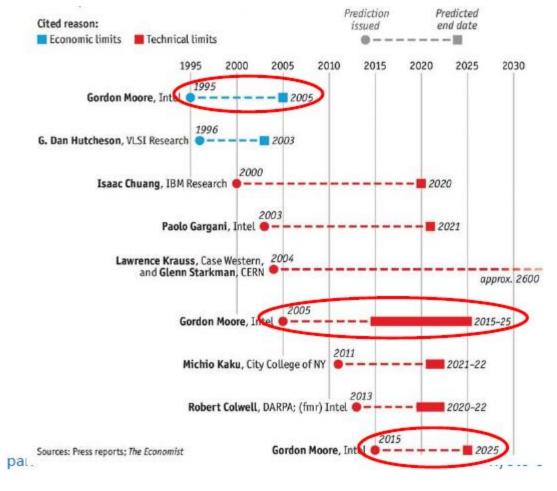

#### Is the End of Moore's Law Coming?

Many predictions of the end of Moore's Law (last prediction by Gordon Moore -> 2025)

Besi

#### **Enhanced Capabilities Demanded**

# **Current Integration Architectures**

**Future Integration Architectures**

**Demand for High Capabilities**

**Disruptive Developments**

#### 2D-Side-by-Side Packages

- Conventional 2D Multi Chip Package architectures, typically FC-BGA,

- Either MR-FC bonding or TC-Bonding

- Interconnection of active side-by-side die is accomplished by either (wire bonded) wires and/or substrate traces

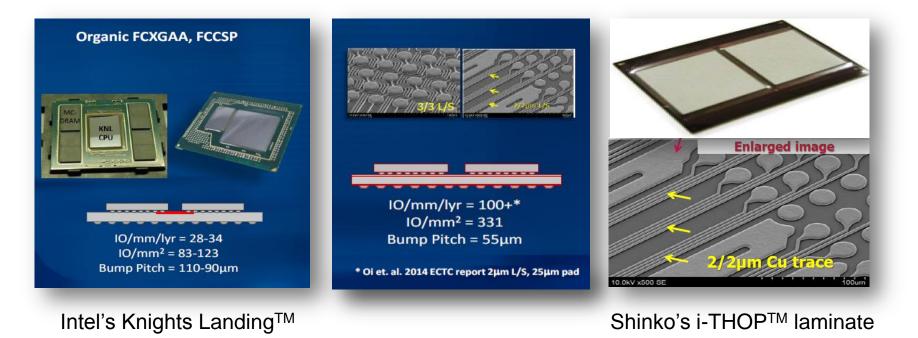

#### **Organic RDL Based Packages**

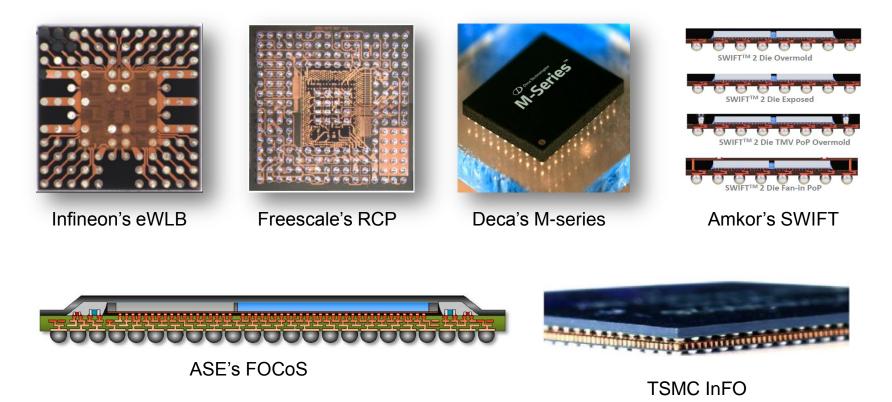

- Organic RDL based WL/PL-Fan-out packaging technology

- Interconnection of active side-by-side die is accomplished by an organic redistribution layer (RDL)

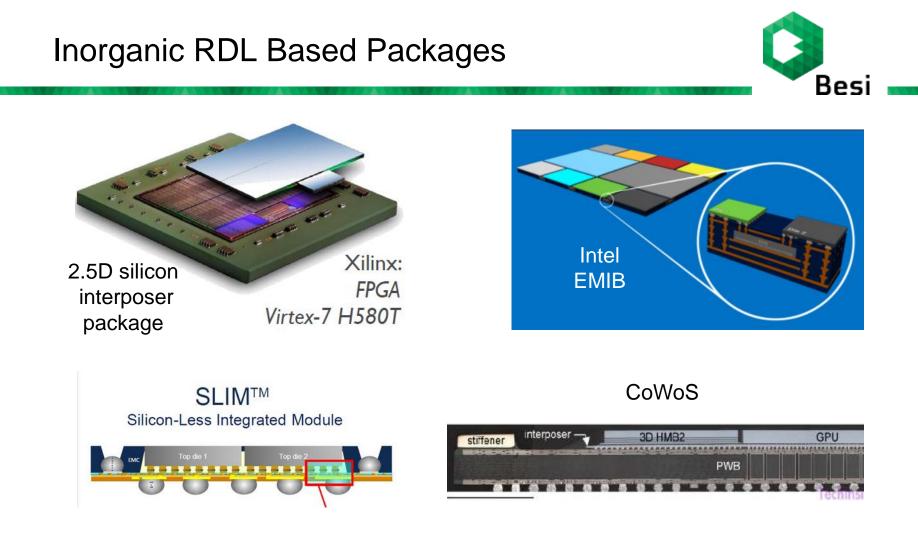

Based on inorganic RDL (silicon oxide, silicon nitride)

- a) 2.5D TSV based or TSV-less silicon or glass interposer packaging

- b) embedded silicon bridges (EMIB<sup>™</sup>)

- c) CoWoS (Chip on wafer on Substrate): 2.5D Si-interposer on substrate

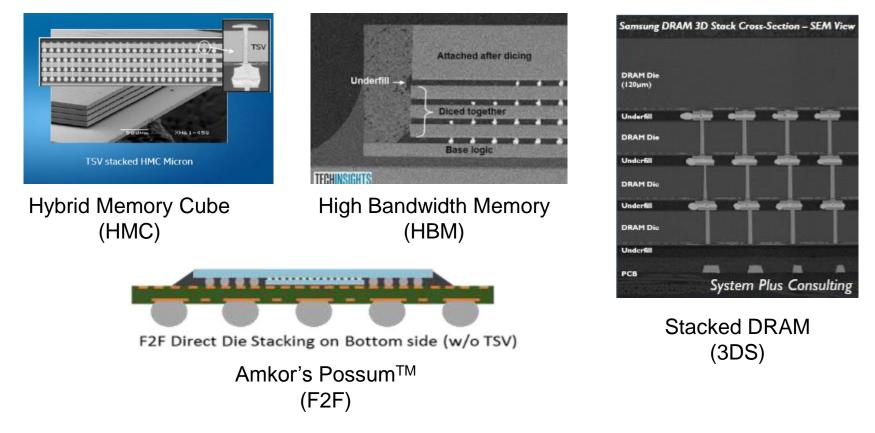

#### 3D-Stacked IC (3D-SIC)

- Direct interconnected active die which are 3D arranged

- a) 3D TSV based packaging

- b) 3D Face-to-face packaging

**Current Integration Architectures**

Besi

**Future Integration Architectures**

**Demand for High Capabilities**

**Disruptive Developments**

|                                    | 3D-SIC                                                                                                                                                     | 3D-SOC                                                                                 |                                                                                              |                                                              |    |

|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|--------------------------------------------------------------|----|

| wiring level                       | Global                                                                                                                                                     | Semi-global                                                                            | Intermediate                                                                                 | Local                                                        |    |

| 2-tier<br>stack                    |                                                                                                                                                            |                                                                                        |                                                                                              | 2 <sup>nd</sup> FEOL<br>after stacking                       | 30 |

| Contact Pitch<br>Relative density: | $\begin{array}{c} 40 \Rightarrow 20 \Rightarrow 10 \Rightarrow 5\mu m \\ {}^{1}\!/_{16} \Rightarrow {}^{1}\!/_{4} \Rightarrow 1 \Rightarrow 4 \end{array}$ | $\begin{array}{ccc} 5 & \Rightarrow \ I \ \mu m \\ 4 & \Rightarrow \ I 00 \end{array}$ | $\begin{array}{ccc} 2 \ \mu m & \Rightarrow 0.5 \ \mu m \\ 50 & \Rightarrow 400 \end{array}$ | $200 \Rightarrow 100 \text{ nm}$<br>$5000 \Rightarrow 10000$ |    |

| Partitioning                       | Die                                                                                                                                                        | blocks of standard cells                                                               |                                                                                              | Gates                                                        |    |

#### IMEC 3D-Roadmap

Besi

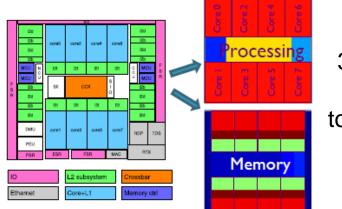

#### **OPENSPARC T2**

3D-SOC Study for OpenSPARC T2 to be 3D-integrated into Logic + Memory

Source: Philipp Absil, "Overview of the 3D Technology Landscape And Challenges", Semicon korea 2016:

#### 2.5D Chiplet (Dielet) Platforms

#### DARPA's CHIPS Program [1]

- CHIPS = chiplet (dielet) platform

- Chiplet = functional, verified, re-usable IP block, realized in physical form [2]

Pitch sweet spot between 2 and 10µm for chiplet (dielet) based HI platforms [3]

Increasing interconnect Pitch

Source:

- [1] D.S. Green, "DARPA's CHIPS Program, and Making Heterogeneous Integration Common", 3D-ASIP 2017

- [2] S. Shumarayev, "Heterogeneous Platform Innovation with Partners", 3D ASIP 2017

- [3] S. Iyer, "3D-SOCs Through Advanced Packaging", 3D-ASIP 2016

Mechanical SoC like Optimal pitch Z-10 µm Die vielding constraint

CMOS Wire - like

Contacted Gate pitch

~50nm

Key constraints: Interconnect pitch and dielet size

500 µm

**BGA/LGA**

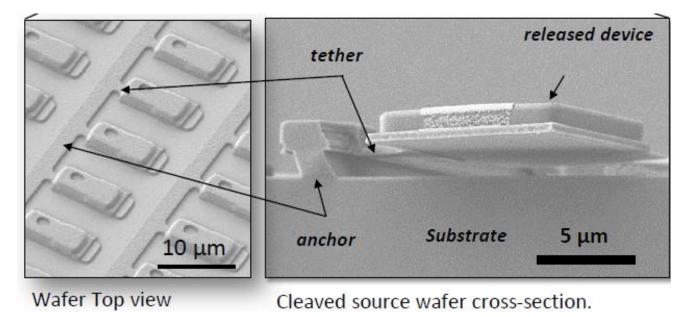

## **Transfer Printing**

- Example of transfer-print compatible micro devices

- Devices are undercut and anchored using MEMS-processing technologies

- Throughput proposals beyond 300.000 components/hour

- 1.5µ @ 3σ accuracy required

Source: Kanchan Ghosal / X-Celeprint: "Mass Transfer of Microscale Devices Using Transfer Printing, 3D ASIP Conference, 2017

**Current Integration Architectures**

**Future Integration Architectures**

**Demand for High Capabilities**

**Disruptive Developments**

### **Drive for Higher Accuracy**

# **Enhanced Capabilities Demanded**

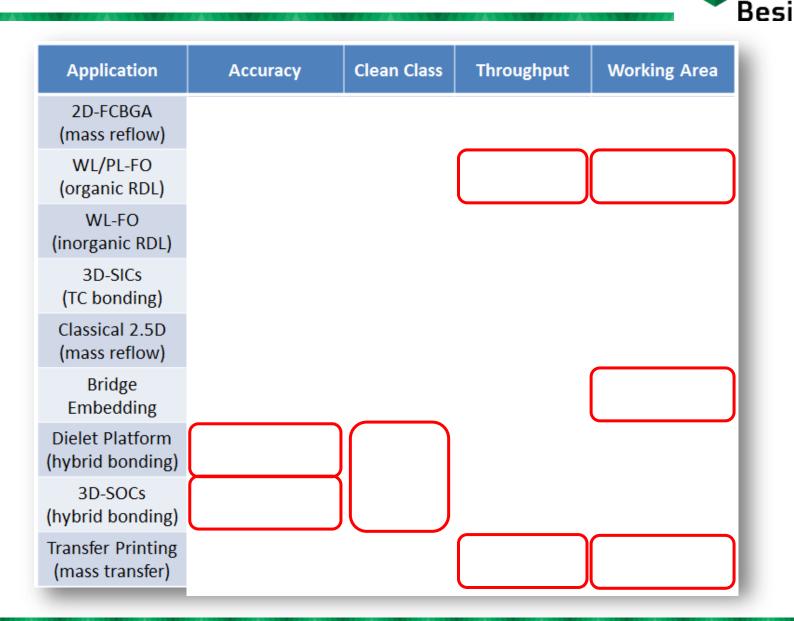

| Application                                   | Accuracy                     | Clean Class      | Throughput                | Working Area                   |

|-----------------------------------------------|------------------------------|------------------|---------------------------|--------------------------------|

| 2D-FCBGA<br>(mass reflow)                     | 5-10μ@3σ<br>(die center)     | ISO-6            | 15-20 kCPH                | 300 x 125 mm                   |

| WL/PL-FO<br>(organic RDL)                     | 3-10μ@3σ<br>(die corners)    | ISO-5            | 15-40 kCPH                | φ 300 mm<br>650 x 550 mm       |

| WL-FO <sup>a)</sup><br>(inorganic RDL)        | 2-3μ@3σ<br>(die corners)     | ISO-5            | 5-10 kCPH                 | ф 300 mm                       |

| 3D-SICs<br>(TC bonding)                       | 2-3μ@3σ<br>(die corners)     | ISO-5            | 3-5 kCPH<br>(tack & gang) | φ 300 mm                       |

| Classical 2.5D <sup>C)</sup><br>(mass reflow) | 3-5μ@3σ<br>(die center)      | ISO-5            | 5-10 kCPH                 | ф 300 mm                       |

| Bridge <sup>b)</sup><br>Embedding             | 0.5-2μ@3σ<br>(die corners)   | ISO-4            | 2-5 kCPH                  | 650 x 550 mm                   |

| Dielet Platform<br>(hybrid bonding)           | 0.2-1μ@3σ<br>(die corners)   | ISO-3<br>(ISO-2) | 5-10 kCPH                 | ф 300 mm                       |

| 3D-SOCs<br>(hybrid bonding)                   | 50-500nm@3σ<br>(die corners) | ISO-3<br>(ISO-2) | 1-5 kCPH                  | φ 300 mm                       |

| Transfer Printing<br>(mass transfer)          | 0.5-2μ@3σ<br>(die corners)   | ISO-5<br>(ISO-4) | 50–300 kCPH               | 650 x 550 mm<br>(920 x 730 mm) |

future ←

> present

May-2018

Besi

**Current Integration Architectures**

Besi

**Future Integration Architectures**

**Demand for High Capabilities**

**Disruptive Developments**

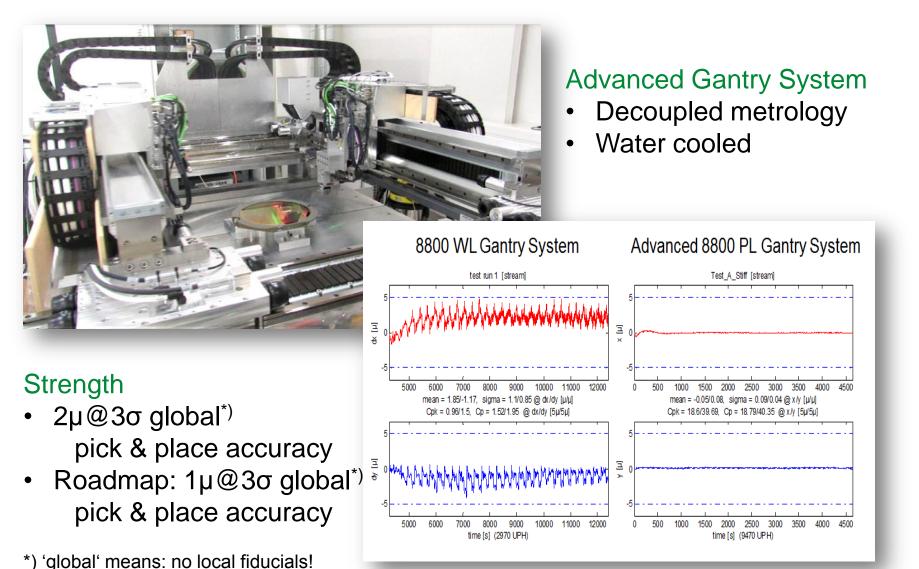

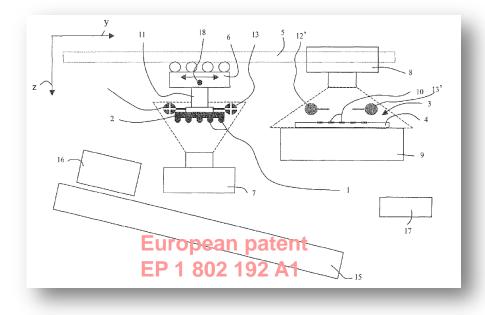

#### **Advanced Gantry System**

To achieve 200nm@3σ placement accuracy (@ 1000 UPH)

## **Principle**

- 1. tool reference marks next to the die

- 2. upward camera determines position of die fiducial relative to tool reference mark

- 3. downward camera determines position of substrate fiducial relative to tool reference mark

- 4. Calculation of resulting misalignment and correction with ,Nano Actor'

Besi

#### **Enhanced Clean Capability**

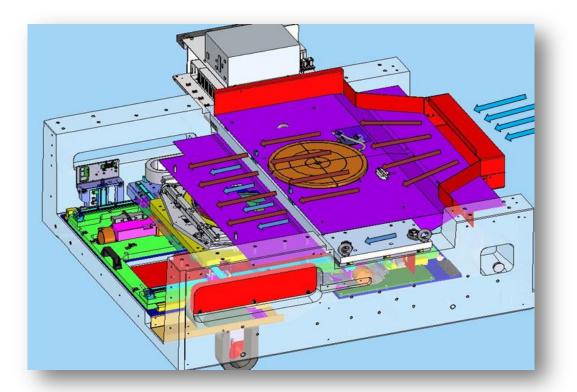

#### ISO-3 clean concept for Datacon 8800 platform

- 1. Use of ISO-3 compatible cables & vacuum hoses

- 2. Covering all energy chains exhaust dirty air from inside of covers

- 3. Introducing horizonal, HEPA filter cleaned laminar flow

- 4. Loading substrate and diced wafers from FOUPs via EFEMs

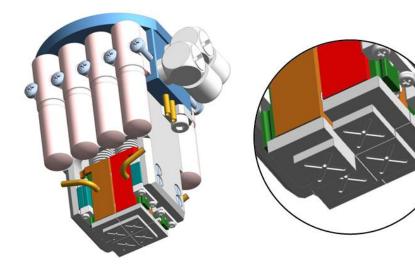

# Parallel Die Processing

Multi-nozzle bond head concept for Datacon 8800 platform

- Common z-axis for 4 nozzles

- Individual mini-stroke per nozzle to move nozzle into working or standby position

#### Throughput Target:

- 20.000+ chips/hour

- \$\$00 or 650x550 mm

- 1. Sequential picking of dies

- 2. Concurrent (parallel) transfer of 4 dies

- 3. Concurrent (parallel) upward vision of 4 dies

- 4. Sequential bonding of dies

**Current Integration Architectures**

Besi

**Future Integration Architectures**

**Demand for High Capabilities**

**Disruptive Developments**

- Advanced Die Attach will be in future a key technology for Heterogeneous Integration.

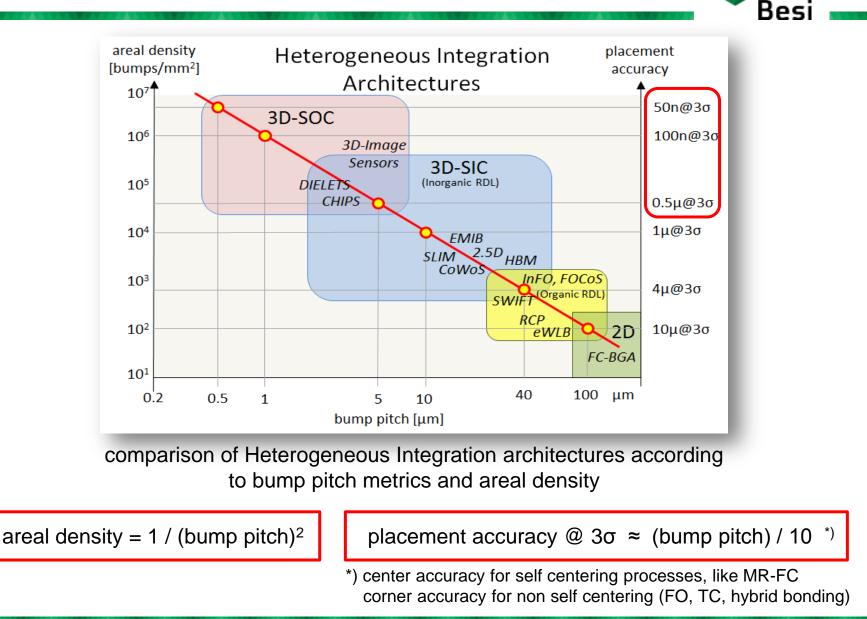

- Roadmaps are proposing 40->10µ pitch for 2.5D/3D SIC, 10-2µ pitch for dielet/chiplet 2.5D platforms, and 5->1µ pitch for 3D-SOCs.

- Hybrid bonding is believed to be the killer technology for sub micron W2W, D2D or D2W 2.5D/3D integration architectures

- hybrid bonding is driving sub-µm placement accuracy with ultra clean conditions (ISO3->ISO2), while cost down drives throughput beyond 20.000 UPH on GEN-3 panel level (650 x 550 mm)

- 4 disruptive developments for Advanced Die Attach

- Water cooled Advanced Gantry System based on decoupled metrology

- 'Van Gogh Alignment' method for nanometer scale placement accuracy

- ISO-3 clean concept for 8800 advanced die attach platform

- Quattro-nozzle bond head for parallel die transfer and sequential pick/place

# Thank You!