# Thermal Sign-Off Analysis for Advanced 3D IC Integration

Dr. John Parry, CEng.

Senior Industry Manager Mechanical Analysis Division

May 27, 2018

## Topics

- Acknowledgements

- Thermal Challenges

- Issues with Existing Solutions

- Thermal Analysis Flow Requirements

- How to Achieve Accuracy

- Early Co-Design Exploration

- Late Co-Design Refinement & Optimization

- Project Saraha Example

- Prediction vs. Experiment

- Questions Answered(?)

### Acknowledgements

- I'd like to thank:

- Pascal Vivet (CEA-Leti, Grenoble) for his kind permission to use material presented at DAC and Mentor U2U conferences

- Lee Wang (Mentor D2S) for her support on the Calibre flow

- Byron Blackmore (Mentor MAD) for his support on FloTHERM.

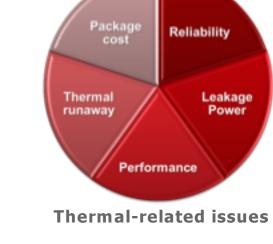

### **Thermal Challenges**

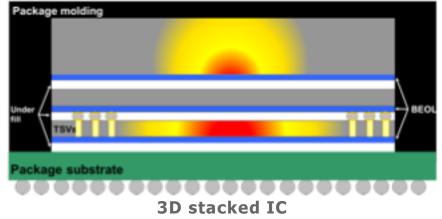

- Thermal issues in 3D ICs:

- Higher power density

- Heat removed through stacked dies

- Die bonding *increases* vertical thermal resistance

- Thinned dies *increases* lateral thermal resistance

- Non-homogeneous distribution of 3D connections

- Dies are becoming more non-uniform in temperature; and

- Dies thermally interact: self-heating is augmented by neighbouring die

### **Issues with Existing Solutions (CAE-Leti view)**

■ "Gaps" in the two main thermal analysis flows:

- 1. Traditional FEM/CFD/Multiphysics simulation tools

- Model setup is complex

- No support for the ASIC design flow

- Generally unable to handle complexity of analysis:

- Number of discrete objects, sources étc.

- Meshing challenges

- Long solution times

### 2. ASIC design flow:

- Poor or no support for 3D integration

- Limited/simplistic support for package

- Inaccurate representation of package boundary conditions

Syntesis

Layout

Block

Diagram

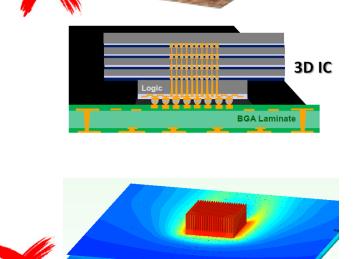

### **Thermal Analysis Flow Requirements**

- Main objective is to support the IC design flow:

Aim to get best overall design, or at least a design that works

- Detailed die-level thermal analysis needs an accurate package model and boundary conditions

Package

- Heat does not respect packaging levels!

- From **Design Exploration** in early design...

- Requires speed and agility

- ... To final Sign-Off

6

- Requires both high accuracy and automation

- UX: Must be compatible with 3D integration technology and integrated into the ASIC design flow.

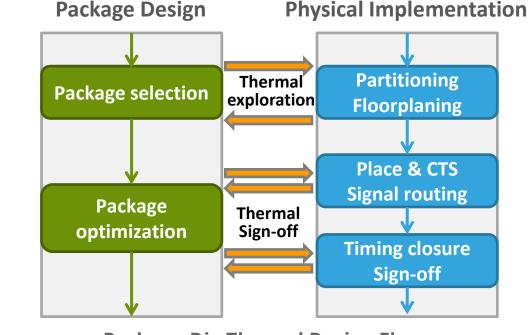

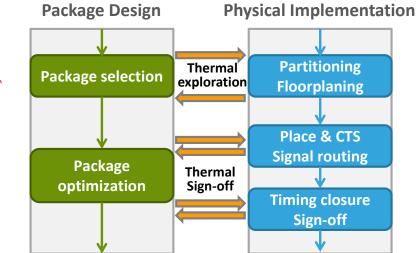

**Package-Die Thermal Design Flow**

#### JDP, Thermal Sign-Off Analysis for Advanced 3D IC Integration, May 2018

### Accuracy and How to Achieve it

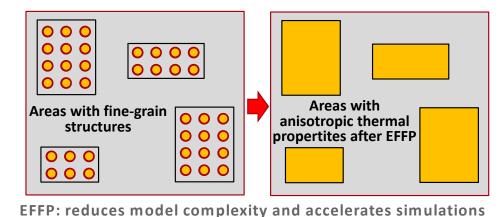

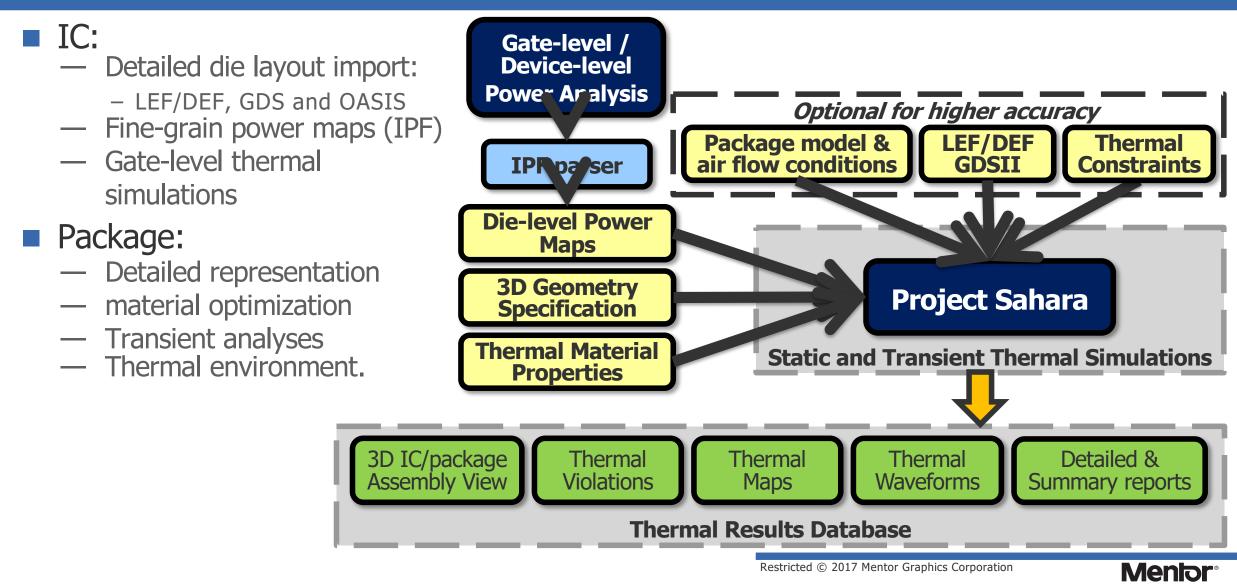

### Effective Thermal Property Extraction from layout (EFFP)

- Compute equivalent anisotropic thermal properties to reduce thermal model complexity

- Dramatic reduction of geometry count leads to significant simulation speed up

- Adjustable granularity for accuracy vs. CPU time trade-off

- Support for IPF: from gate-level/device-level power analysis

- Fine-grain power maps to capture hotspot effects

- Automatic compression of power sources in very high instance count designs to accelerate simulation

#### Automation

- Automatic constraint checks to avoid error-prone and time-consuming manual verification of thermal constraints

- Fast, automatic gridding and automatic time step generation for thermal analysis

Hotspots in nonuniform power distribution captured in gate-level thermal analysis

JDP, Thermal Sign-Off Analysis for Advanced 3D IC Integration , May 2018

### Early Co-Design: Design Space Exploration

### IC:

- 3D partitioning,

- Chiplet placement

- Die-die interface layer design

- Block and TSV floorplans,

- Package selection

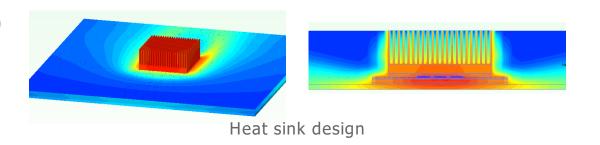

#### Package/Board/Heatsink:

- Package I/O connection to board layers

- Package design exploration (e.g. copper lid)

- Optimization of TIM layers

- Heatsink design (e.g. base thickness).

### Late Co-Design: Refinement & Design Optimization

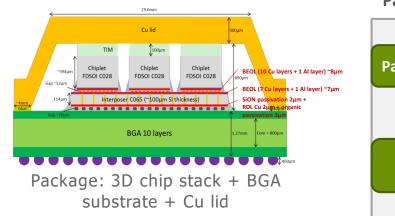

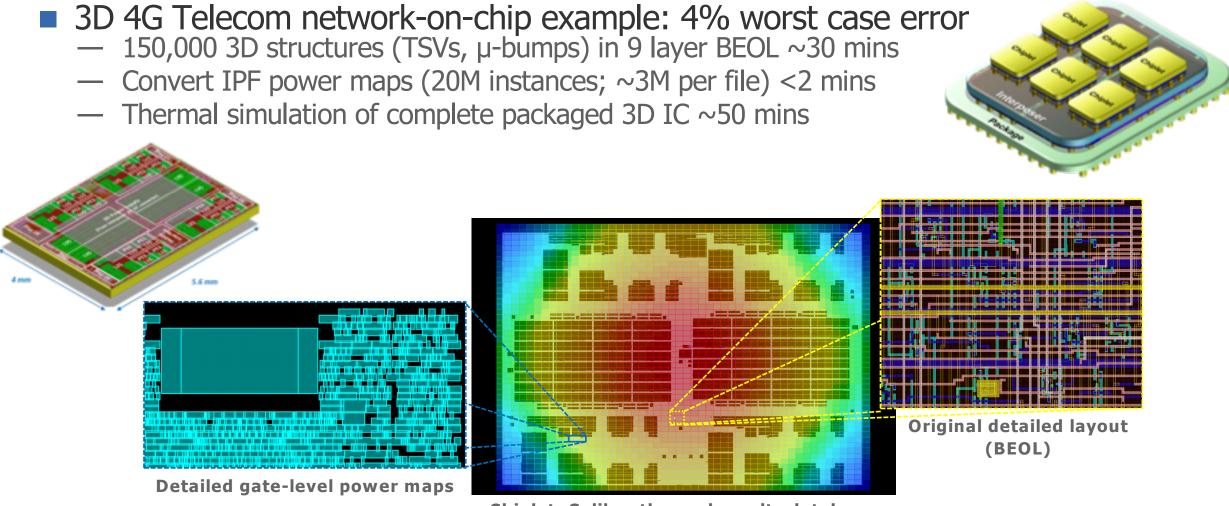

### **Project Sahara Example from CEA Leti**

Chiplet: Calibre thermal results database

### **Questions Answered(?)**

- 1. What is the state-of-the-art in co-design?

- For IC/package thermal co-design, broadly what has been covered here

- Thermal IC/package co-design is moving from research into use in design

- Fast, fine-detail analysis is possible

- High level of automation can be achieved in both simulation and rule checking

- 2. What key challenges need to be overcome?

- Technically, thermal co-design is feasible today

- Main challenge is awareness raising:

- Need to do thermal design is often not recognized (until it is too late)

- After 30 years, people are still using  $\Theta_{JC}$  in hand calculations for system design

- 3. What needs to happen for these challenges to be overcome?

- IEEE Heterogeneous Integration Roadmap will help raise awareness of the challenges, and give pointers to possible solutions.