# Power Electronic Packaging, Co-Design and Reliability

Yong Liu, Corporate R & D May 29, 2018

**ON Semiconductor®**

2018 IEEE 68th Electronic Components and Technology Conference | San Diego, California | May 29 – June 1, 2018

# Outline

- I. Power Electronics Packaging

- II. Current State of Art Co-Design in Power

Electronics Packaging

- III. Challenges in Co-Design and Reliability

- IV. What is the Next?

- V. Summary

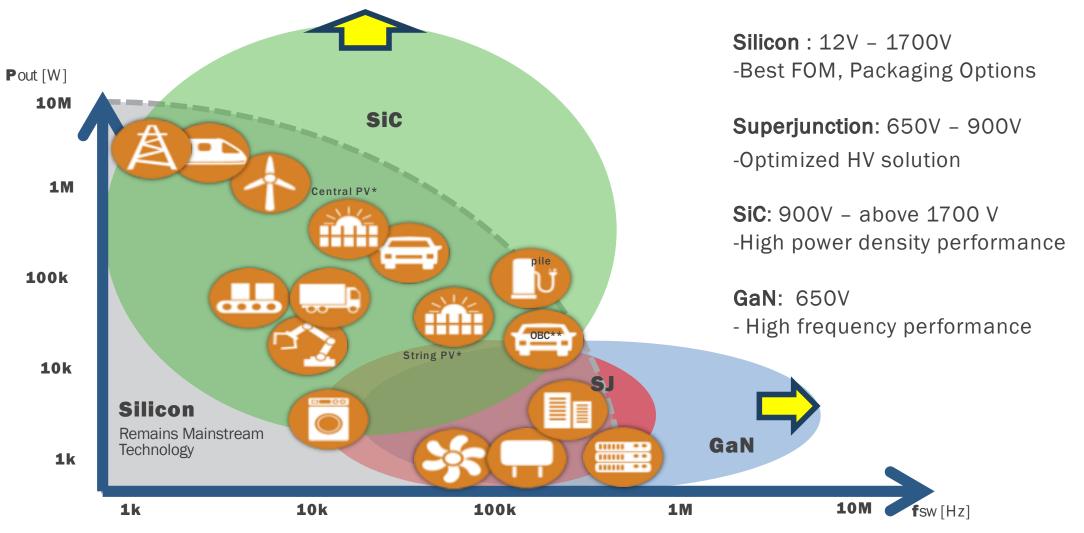

#### I. Power Electronic Packaging: Driven Capability

\* PV = photovoltaic inverter; \*\* OBC = onboard charger

#### I. Power Electronic Packaging: GaN & SiC Applications

650 V SJ MOSFETs 650 V Si/SiC Rectifiers/FETs Automotive HV module 650 V IGBTs 650 V GaN transistors DC-DC, LDO, IVN, ASIC

> Battery Management • 40 V FETs (lowest RDSON)

650/1200 V IGBTs 650 V GaN transistors

#### 12 V, 48 V DC-DC

80/100 V FETs Half-bridge drivers (high speed) 40 V FETs **Op-amps & current sense** DC-DC, LDO, IVN, ASICs

- High Efficiency

- High Reliability

- Low Power Loss

ads

650 V SJ MOSFETs

650 V Si/SiC

**Rectifiers/FETs**

650 V IGBTs

650 V GaN transistors Automotive modules

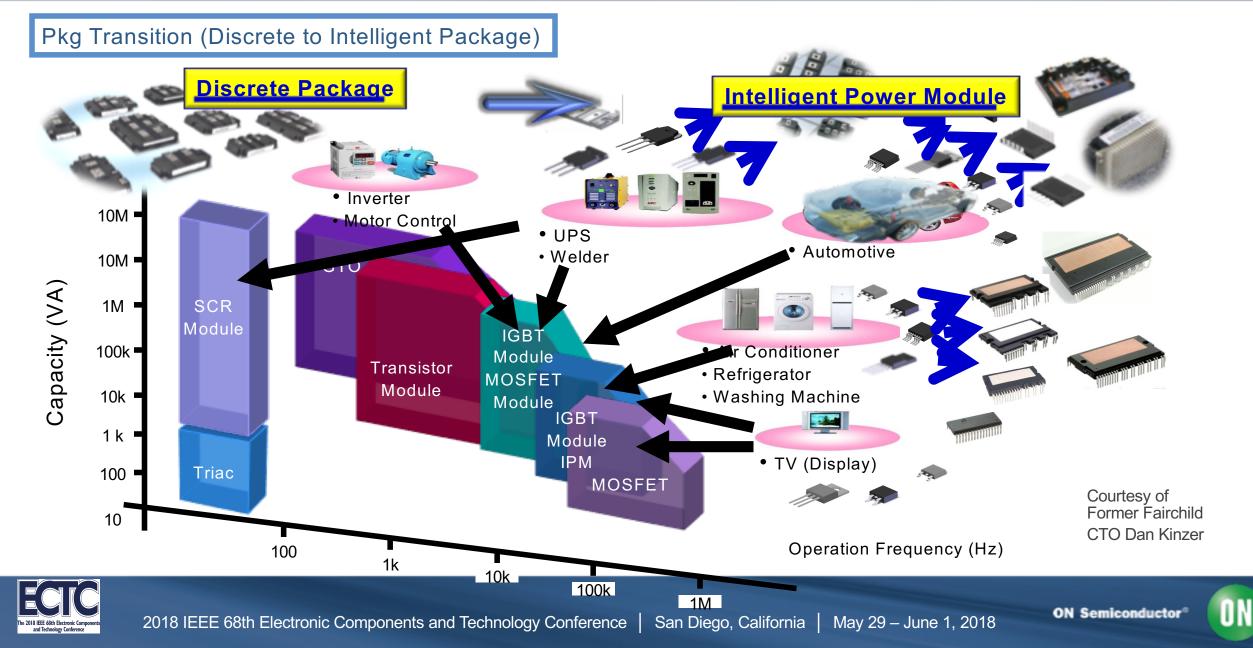

### I. Power Electronic Packaging: Evolution

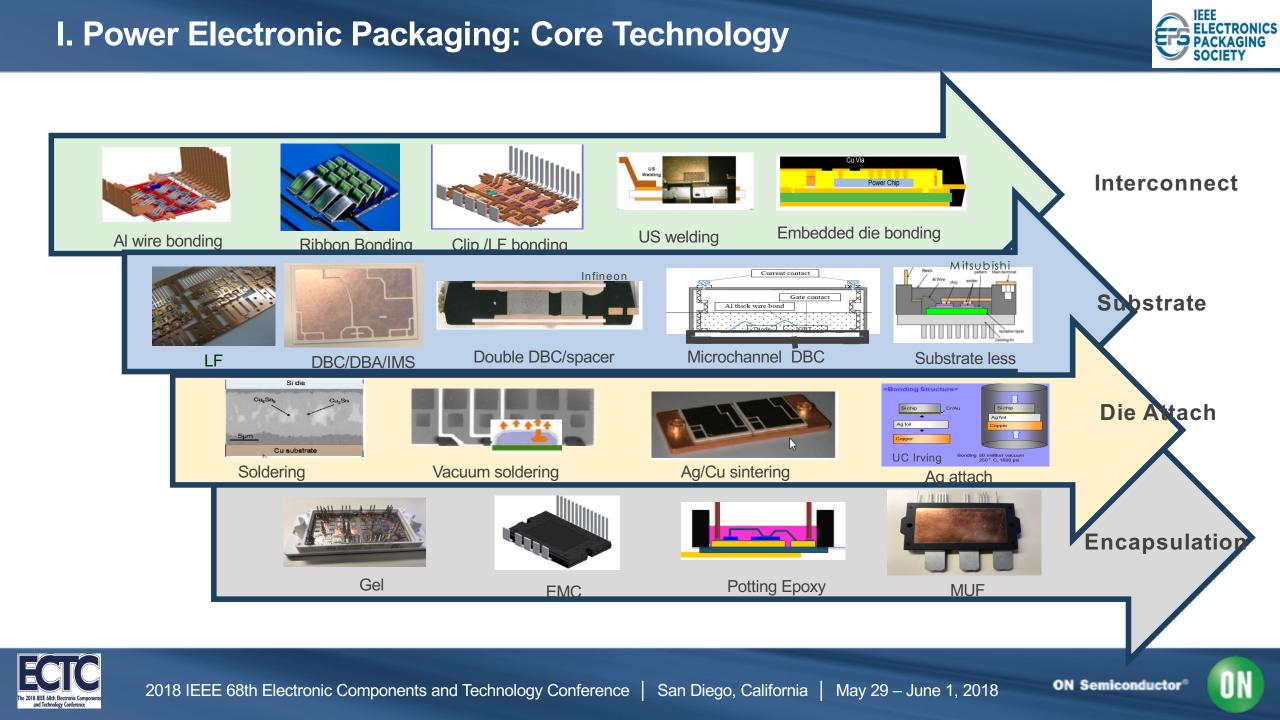

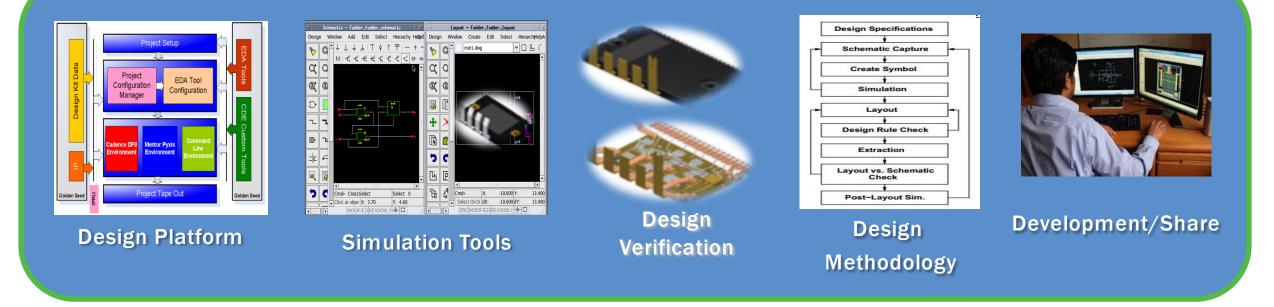

# II. Current State of Art Co-Design in Power Electronic Packaging

- ELECTRONICS PACKAGING SOCIETY

- To Provide Differentiating & Cost Effective Co-design Infrastructure for Power Electronics

- Current Co-Design Platform Includes:

#### Explore/Design + Simulation + Design Verification + Methodology + Development/Share

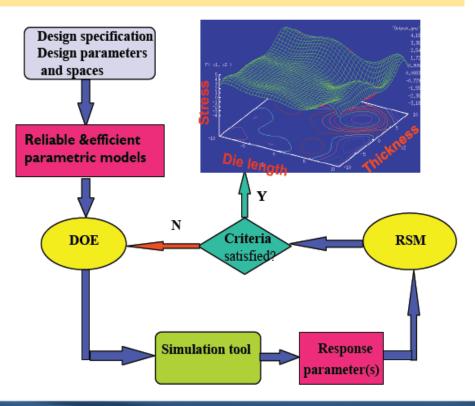

Weakness: Case by Case Not strong in design sensitivity, optimization and probability Not Yet Ready for virtual prototyping

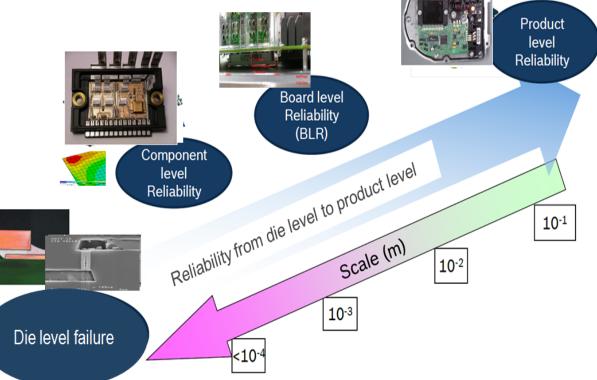

Multi-Scale and Multi-Physics in Co-Design/Reliability: Reliability from Die design to system

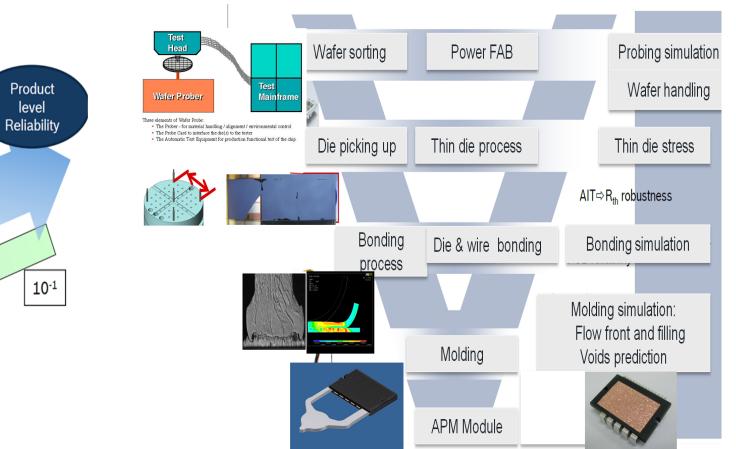

**Assembly Reliability:** Multi-Step Process/Variation/Probability

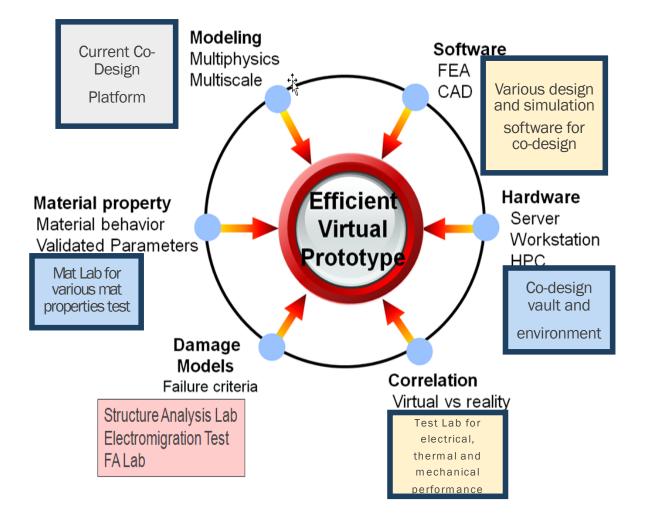

## **IV. What is the next**: Co-Design Ecosystem for a Efficient Virtual Prototype

#### **Co-design ecosystem**

The system will target:

- Multi-scale and Multi-physics in Design

- Sensitivity/Optimization/Probabilistic Analysis • in Design, Assembly Process and Reliability

2018 IEEE 68th Electronic Components and Technology Conference San Diego, California May 29 – June 1, 2018

## V. Summary

- Current state of art Co-Design includes Explore/Design + Simulation + Design Verification + Methodology + Development/Sharing

- Key Challenges in Co-Design/Reliability include Multi-Scale and Multi-Physics, Multi-Step Process/Variation Probability

- Co-Design Ecosystem & Virtual Prototyping will happen soon in Power Electronics Industry

#### **Virtual Prototyping**

Early design phase - Electrical simulation

- Thermal simulation

Virtual characterization

- Thermal and mechanical

stress simulation for

typical performances

- Typical assembly process

- Mold flow simulation

- DFM

Reliability - Virtual BLR

- DFR

Customer support

Thermal simulation

PQA simulation support

Mounting process simulation

Assembly Process Modeling

#

# The second second

#### ECCIC The 2018 IEEE 68th Electronic Components and Technology Conference

2018 IEEE 68th Electronic Components and Technology Conference | San Diego, California | May 29 – June 1, 2018 ON

**ON Semiconductor**