# **Advance Program & Registration**

Don't miss out on electronic packaging's premier conference!

The 2020 IEEE 70th Electronic Components and Technology Conference

# May 26 - May 29, 2020

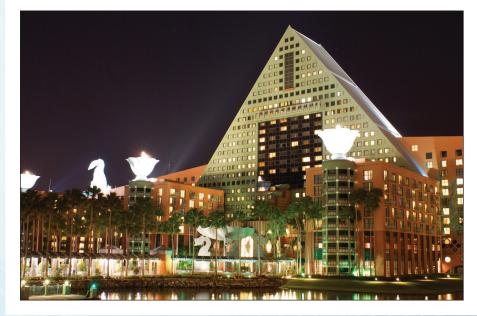

# Walt Disney World Swan & Dolphin Resort Lake Buena Vista, Florida

For more information, visit: www.ectc.net

**Sponsored by:**

ELECTRONICS PACKAGING SOCIETY

# **INTRODUCTION FROM THE IEEE 70TH ECTC PROGRAM CHAIR ROZALIA BEICA**

The 70th Electronic Components and Technology Conference (ECTC) Walt Disney World Swan and Dolphin Resort, Lake Buena Vista, FL USA • May 26 - May 29, 2020

On behalf of the Program and Executive Committees, it is my pleasure to invite you to IEEE's 70th Electronic Components and Technology Conference (ECTC), which will be held at Walt Disney World Swan and Dolphin Resort, Lake Buena Vista, Florida, USA from May 26 - 29, 2020. This premier international annual conference, sponsored by the IEEE Electronics Packaging Society (EPS), brings together key stakeholders of the global microelectronic packaging

industry, such as semiconductor and electronics manufacturing companies, design houses, foundry and OSAT service providers, substrate makers, equipment manufacturers, material suppliers, research institutions, and universities, all under one roof. More than 1,500 people have attended ECTC in each of the last three years.

At the 70th ECTC, around 380 technical papers are scheduled to be presented in 36 oral sessions and five interactive presentation sessions, including one interactive presentation session exclusively featuring papers by student authors. The oral sessions will feature selected papers on key topics such as wafer-level and fan-out packaging, 2.5D, 3D and heterogeneous integration, interposers, advanced substrates, assembly, materials modeling, reliability, packaging for harsh conditions, power packaging, interconnections, packaging for high speed and high bandwidth, photonics, and flexible and printed electronics. Interactive presentation sessions will showcase papers in a format that encourages more in-depth discussion and interaction with authors about their work. Authors from over twenty countries are expected to present their work at the 70th ECTC, covering ongoing technology development within established disciplines or emerging topics of interest for our industry such as additive manufacturing, heterogeneous integration, flexible and wearable electronics.

ECTC will also feature six special sessions with invited industry experts covering several important and emerging topic areas. On Tuesday, May 26 at 9:30 a.m., Pavel Roy Paladhi and Nicholas Bronn will chair a special session covering "Bridge to Quantum Computing," On the same day at 2 p.m., Rena Huang and Harry Kellz will chair a session focusing on "Cutting-Edge Technology on Integrated Photonics and Packaging." Tuesday evening will also include the ECTC Panel Session at 7:30 p.m. chaired by IEEE EPS President Christopher Bailey and Karlheinz Bock, where young researchers will share their visions of future packaging technologies and participate in discussions with experts in the field.

This conference will also feature our prestigious Luncheon Keynote on Wednesday, May 27. We are pleased to have Douglas Yu from Taiwan Semiconductor Manufacturing Company addressing new and innovative packaging technologies. His talk is titled "Innovative Heterogeneous Integration Technologies Initiate a New Semiconductor Era."

We are continuing our tradition and bringing back the networking events focused on young professionals and diversity. Adeel Bajwa will chair on Tuesday, May 26, 6:30 p.m. the Young Professional Panel. The Diversity and Career focused Panel and Reception, jointly organized by ECTC and ITherm, will take place on Wednesday, May 27 at 6:30 p.m. The panel will be chaired by Kitty Pearsall and Cristina Amon and will focus on some of the specifics of inclusion in a diverse workforce. On the same day at 7:30 p.m., Michael Mayer will chair the ECTC Plenary Session titled "3DIC: Past, Present and Future." In this plenary session, experts will address the evolution of 3D integration, new applications and opportunities for using 3DIC technology as well as its challenges along the value chain. On Thursday, May 28 at 8 p.m., the IEEE EPS Seminar entitled "Future Semiconductor Packages for Artificial Intelligence Hardware" will be moderated by Yasumitsu Orii and Shigenori Aoki. The seminar will focus on brain inspired devices and integration technologies.

Supplementing the technical program, ECTC also offers Professional Development Courses (PDCs) and Technology Corner exhibits. Co-located with the IEEE ITherm Conference, the 70th ECTC will offer eighteen PDCs, organized by the PDC Committee chaired by Kitty Pearsall and Jeffrey Suhling. The PDCs will take place on Tuesday, May 26 and are taught by distinguished experts in their respective fields. The Technology Corner exhibits will showcase the latest technologies and products offered by leading companies in the electronic components, materials, packaging, and services fields. More than one hundred Technology Corner exhibits will be open Wednesday and Thursday starting at 9 a.m. ECTC also offers attendees numerous opportunities for networking and discussion with colleagues during coffee breaks, daily luncheons, and nightly receptions.

Whether you are an engineer, a manager, a student, or an executive, ECTC offers something unique for everyone in the microelectronics packaging and components industry. I invite you to make your plans now to join us for the 70th ECTC and to be a part of all the exciting technical and professional opportunities. I also take this opportunity to thank our sponsors, exhibitors, authors, speakers, PDC instructors, session chairs, and program committee members, as well as all the volunteers who help make the 70th ECTC a success. I look forward to meeting you in Lake Buena Vista, Florida, on May 26 –29, 2020.

Rozalia Beica 70th ECTC Program Chair AT&S Email: rbeica.semi@gmail.com

# Index

| ECTC Registration                                               |

|-----------------------------------------------------------------|

| General Information                                             |

| Hotel Information                                               |

| 2020 Photonics Special Session4                                 |

| 2020 ECTC Special Session4                                      |

| 2020 ECTC Panel Session4                                        |

| 2020 ECTC Plenary Session4                                      |

| 2020 Young Professionals Networking Panel4                      |

| 2020 ECTC/ITherm Diversity and Career Growth Panel & Reception5 |

| 2020 Florida Photonics Cluster Session                          |

| 2020 IEEE EPS Seminar5                                          |

| ECTC Luncheon Keynote Speaker6                                  |

| Luncheons and Receptions                                        |

| Executive and Program Committees7-8                             |

| Professional Development Courses9-14                            |

| Area Attractions                                                |

| Program Sessions                                                |

| 2020 Technology Corner Exhibits                                 |

| Conference Overview                                             |

# **70th ECTC ADVANCE REGISTRATION**

### **Advance Registration**

# Online registration is available at www.ectc.net. For more information on registration rates, terms, and conditions see page 32.

Register early ... save US\$100 or more! All applications received after May 4, 2020, will be considered Door Registrations. Those who register in advance can pick up their registration packets at the ECTC Registration Desk in the Dolphin Convention Center on the Lobby Level in front of Australia 3. *Please note that the Swan and Dolphin are two separate buildings, and all ECTC meetings will be taking place in the Walt Disney World Dolphin Resort.*

#### **On-Site Registration Schedule**

Registration will be held in the Dolphin Convention Center on the Lobby Level in front of Australia 3.

Monday, May 25, 2020

3:00 p.m. - 5:00 p.m.

Tuesday, May 26, 2020

6:45 a.m. - 5:00 p.m.\*

\*6:45 a.m. - 8:00 a.m.: Moming PDCs & moming ECTC Special Session only

Wednesday, May 27, 2020

6:45 a.m. - 4:00 p.m.

Thursday, May 28, 2020

7:30 a.m. - 4:00 p.m.

Friday, May 29, 2020

7:30 a.m. - 12:00 Noon

The above schedule for Tuesday will be rigorously enforced to prevent students from being late for their courses.

# **General Information**

Conference organizers reserve the right to cancel or change the program without prior notice. \*\*Please note that the Walt Disney World Swan and Dolphin Resort are two separate buildings, and ALL ECTC meetings will be taking place in the Walt Disney World Dolphin Resort. While booking your hotel reservation, please make sure to specify that you require to be placed in the Walt Disney World DOLPHIN Resort. While these two buildings are located adjacent to each other and share many of the same social / resort function areas, we want to ensure you have a very convenient experience while at ECTC 2020.\*\*

#### ITherm 2020

This year ITherm is co-located with ECTC! All ITherm sessions will take place in the SWAN building of the Walt Disney World Swan and Dolphin Resort. ALL ECTC sessions, and the co-location of exhibits, will take place in the DOLPHIN building!

# Loss Due to Theft

Conference management is not responsible for loss or theft of personal belongings. Security for each individual's belongings is the individual's responsibility.

#### **ECTC Sponsors**

With 69 years of history and experience behind us, ECTC is recognized as the premier semiconductor packaging conference and offers an unparalleled opportunity to build relationships with more than 1,500 individuals and organizations committed to driving innovation in semiconductor packaging.

We have a limited number of sponsorship opportunities in a variety of packages to help get your message out to attendees. These include Platinum, Gold, Silver, Special and Program Sponsors, and several other sponsorship options that can be customized to your company's interest. If you would like to enhance your presence at ECTC and increase your impact with a sponsorship, please take a look at our sponsorship brochure on the website www.ectc.net under "Sponsors."

To sign-up for sponsorship or to get more details, please contact Wolfgang Sauter at wsauter2@gmail.com or +1-802-922-3083.

### **Hotel Accommodations**

Rooms for ECTC attendees have been reserved at the Walt Disney World Dolphin, of the Walt Disney World Swan and Dolphin Resort. The special conference rate is:

# \$199.00 / Run of the House + \$14 Resort Services Fee Daily

Please note these rooms are on a first-come, first-served basis. If this specific category is no longer available, attendees will be offered the next best available accommodation. These prices include single or double occupancy in one room. Please note that rooms offering two beds are limited and subject to availability and should be requested at the time of reservations.

The conference rate of \$199/night will only be available until Friday, May 1, 2020 at 5pm ET or until rooms run out, whichever comes first. To ensure our preferred conference rate, please make your reservation online through **www.ectc.net** or by directly contacting the hotel. All reservations made after the conference rate is no longer available will be accepted on a space and rate available basis. If you need to cancel a reservation, please do so AT LEAST 5 DAYS prior to arrival for a full refund. Each attendee is subject to the terms and policies set by each hotel.

### **Note about Hotel Rooms**

Attendees should note that only reputable sites should be used to book a hotel room for the 2020 ECTC. Be advised that you may receive emails about booking a hotel room for ECTC 2020 from 3<sup>rd</sup> party companies. These emails and sites are not to be trusted. The only formal communication ECTC will convey about hotel rooms will come in the form of ECTC e-blasts or ECTC emails from our Executive Committee. ECTC's only authorized site for reserving a room is through our website (**www.ectc.net**). You may, however, use other trusted sites that you personally have used in the past to book travel. Please be advised, there are scam artists out there, and if it's too good to be true, it likely is. Should you have any questions about booking a hotel room, please contact ECTC staff at: **Irenzi@renziandco.com**

#### **Transportation Services**

Enjoy a complimentary water taxi from the resorts' dock, running to and from **Epcot**® and **Disney's Hollywood Studios™**.

Complimentary shuttle buses also transport guests from the hotel entrance to Magic Kingdom® Park, Disney's Animal Kingdom® Theme Park, Downtown Disney® area, and Disney' Blizzard Beach Water Park, and Disney's Typhoon Lagoon Water Park.

There is, unfortunately, no courtesy transportation between the hotel and the airport.

# 2020 ECTC Special Session

Bridge to Quantum Computing Tuesday, May 26, 2020, 9:30 a.m. – 11:30 a.m. Chairs: Nicholas Bronn – IBM Research and Pavel Roy Paladhi – IBM Systems

Quantum computers can provide a platform to solve hard problems which are computationally intractable with traditional computer architecture. Research on quantum computing over the past few decades has led to many breakthroughs and as a result, the field of quantum computing has come to a stage where implementing quantum computers to solve real life problems on a large scale is drawing nearer and nearer. However, to exploit the full potential of this emerging field, quantum computing needs to seamlessly integrate with traditional computer hardware and architecture. This session will focus on quantum computer systems and how they relate to traditional computing systems. Areas that need to be researched and tailored to prepare for large scale quantum computation implementation of higher time complexity algorithms will be identified. Aspects of both hardware and software development will be

explored. Experts from the industry and academia will present and discuss some of the key challenges and directions that the research should be focused on. It is anticipated that this topic will become very significant to the computer packaging industry as well as the quantum computing world and this panel gives an opportunity for the ECTC community to be informed and ready to contribute.

- 1. Nicholas Bronn IBM Research, Yorktown Heights

- 2. Prof. Paul Franzon North Carolina State University

- 3. Amir Jafari-Salim SeeQC

- 4. Rabindra Das MIT Lincoln Laboratory

### **2020 Photonics Special Session**

Cutting-Edge Technology on Integrated Photonics and Packaging Tuesday, May 26, 2020, 2:00 p.m. – 4:30 p.m. Chairs: Rena Huang – Rensselaer Polytechnic Institute and Harry Kellzi – Micropac Industries

The special session aims to capture the latest technology advancements in the fast evolving photonics areas that have wide interest to industry, academia and government laboratories worldwide. The session will comprise of two sub-sections focused on photonic integrated circuits and wideband RF over fiber circuits:

• *Photonic Integrated Circuits (PICs)* will focus on the integration of photonic integrated functions of both active and passive functions developed both in Indium Phosphide (InP) and Silicon wafer technologies for information signals transmission applications, such as tunable lasers, modulated lasers and transmitters and integrated receivers.

• Wideband RF over Fiber Circuits will address the conversion of electronics and electromagnetics traditional copper to light over wideband Fiber

transmission with maximum BW, Low Noise Figure and High dynamic range of various applications, such as Microwave links, SATCOM, Wireless communications and others.

Invited speakers will discuss various photonic related topics, sharing their visions on the technology advancement and future trends.

- 1. Kazuhiko Kurata AlO Core, Photonics Electronics Technology Research Association

- 2. M. J. Soileau CREOL, The College of Optics and Photonics, University of Central Florida

#### 2020 Young Professional Networking Panel

Tuesday, May 26, 2020, 6:30 p.m. - 7:45 p.m.

Chair: Adeel Bajwa - Kulicke and Soffa Industries Inc.

#### PANELISTS: EPS Board of Governors members

Chris Bailey, David McCann, Sam Karikalan, Ravi Mahajan, Jeff Suhling, Pat Thompson, Alan Huffman, Kitty Pearsall, Eric Perfecto, Avi Bar-Cohen, William Chen and Subramanyan S. Iyer

This event is designed just for you – young professionals (including current graduate students). In this active event, we will pair you with senior EPS members and professionals through a series of active and engaging activities. You will have opportunities to learn more about packaging-related topics, ask career questions, and meet some professional colleagues.

# 2020 ECTC Panel Session

Future (Visions) of Electronics Packaging Tuesday, May 26, 2020, 7:30 p.m. – 9:00 p.m. Chairs: Christopher Bailey, EPS President – University of Greenwich and Karlheinz Bock – TU Dresden

# 2020 ECTC Plenary Session

#### 3DIC: Past, Present and Future Wednesday, May 27, 2020, 7:30 p.m. – 9:00 p.m. Chair: Michael Mayer – University of Waterloo

Driven by the ever increasing degree of miniaturization and the need for lower cost, researchers and visionaries in the manufacturing of microelectronics hardware have thought of extending planar integrated circuits (ICs) into the third dimension. Such 3D IC have been the source of inspiration for technologies such as stacked die and through-silicon-via (TSV). Challenges include process economics and the power/

cooling tradeoff. This plenary session explores the evolution and state of the art of semiconductor 3D technology and discusses details of its current challenges and future promise.

- 1. Douglas Yu TSMC

- 2. Eric Beyne IMEC

- 3. Mitsumasa Koyanagi Tohoku University

- 4. Peter Ramm Fraunhofer Research Institution for Microsystems and Solid State Technologies EMFT

Additional speakers will be announced at a later date.

# 2020 ECTC/ITherm Diversity and

# **Career Growth Panel and Reception**

Diversity and Inclusion Drives Innovation and Productivity Wednesday, May 27, 2020, 6:30 p.m. – 7:30 p.m. Chairs: Kitty Pearsall – Boss Precision, Inc. and Cristina Amon – University of Toronto

Diversity in today's workplace and academia must be more inclusive than just race, gender, and ethnicity. There are religious, political, educational, and cultural differences. Adding to this mix are varied socioeconomic backgrounds, sexual orientation, and people with disabilities. The GDP (Global Diversity Practice) Consultancy Group puts forth the following. "Openness to diversity widens our access to the best talent. Inclusion allows us to engage talent effectively. Together, this leads to enhanced innovation, creativity, productivity, reputation, engagement and results." The panel will discuss their experiences, challenges and best practices that have delivered positive outcomes.

1. Amy S. Fleischer — California Polytechnic State University

Additional speakers will be announced at a later date.

# 2020 Florida Photonics Cluster Session

Research, Manufacturing and Applications of Advanced Photonics Technologies within the Florida Photonics Cluster Thursday, May 28, 2020, 9:00 a.m. – 11:00 a.m. Chairs: Xiaoming Yu – CREOL, College of Optics & Photonics, University of Central Florida

This special session will highlight ongoing activities within the Florida Photonics Cluster (FPC). The mission of FPC is to support the growth and profitability of the photonics industry through the strength of a unified voice and to make Florida the place to go for photonics solutions. Speakers from universities, institutes and industries will be invited in a panel discussion to introduce the recent progress related to the research, design, manufacturing, and

applications of photonics technologies. Speakers will be announced at a later date.

# 2020 IEEE EPS Seminar

Future Seminconductor Packages for Artificial Intelligence Hardware Thursday, May 28, 2020, 8:00 p.m. – 9:30 p.m. Chairs: Yasumitsu Orii - Nagase, Japan and Sheigenori Aoki - Fujitsu

An overwhelming amount of data is generated daily, out of which 90% is unstructured. Such data cannot be easily stored in a traditional column-row database, therefore, it is not easily searchable and more difficult to analyze. Today, artificial intelligence (AI) has the ability to analyze unstructured data, however, it also requires a high amount of energy. AI is expected to become one of the biggest energy consumers on the planet. A brain-inspired devices and quantum devices are very attractive to support a future AI due to its low power consumption. In this session, the panelists will discuss the future semiconductor packages in the era of a brain-inspired devices and quantum devices.

To show the product requirements:

- 1. Hiroyuki Akinaga The National Institute of Advanced Science and Technology (AIST)

- 2. Rama Divakaruni IBM T. J. Watson Research, Albany NY

- 3. Subramanian S. Iyer University of California, Los Angeles, "CHIPS"

- Swaminathan Madhavan Georgia Institute of Technology

- 5. Takashi Hisada IBM Research Tokyo

# **ECTC Luncheon Keynote**

# Innovative Heterogeneous Integration Technologies Initiate a New Semiconductor Era Wednesday, May 27, 2020

Douglas Yu – Taiwan Semiconductor Manufacturing Company

In the supply chain for IC, which follows the path of Moore's Law with system-on-chip, packaging technology used to play mainly a protection role. Chip scaling is becoming more challenging and, at the same time, integration of more functions such as memory, sensors and passives, as well as other components for new applications such as AI and 5G, etc. is required. Innovative heterogeneous integration technologies are being proposed for system-on-package to provide

critical Performance, Power and Area (PPA) values for the micro-systems. New, far-reaching changes are being made, which initiate an exciting new semiconductor era and create a new industry landscape.

Mark Your Calendar for ECTC 2021 Sheraton San Diego Hotel and Marina San Diego, California, USA June 1-4, 2021

# Luncheons

# **Tuesday PDC Luncheon**

All individuals attending a PDC are invited to join us for lunch. Proctors and instructors are welcome, too! Those attending a special session on Tuesday may purchase a lunch ticket for \$65 on our website

# Wednesday Conference Luncheon

Please be sure not to miss our Wednesday luncheon with guest speaker Douglas Yu, Vice President of Research and Development from TSMC. All conference attendees are welcome!

# Thursday EPS Luncheon

Our sponsor, the IEEE Electronics Packaging Society, will be sponsoring lunch on Thursday for all conference attendees!

# Friday Program Chair Luncheon

Please attend Friday's lunch hosted by the 70th ECTC Program Chair. We will honor conference paper award recipients and raffle off a vast array of prizes including a hotel stay, free conference registrations, and many other attractive items!

# **General Chair's Speakers Reception**

**Tuesday, May 26, 2020 • 6:00 p.m. – 7:00 p.m.** (by invitation only)

# **ECTC Student Reception**

Tuesday, May 26, 2020 • 5:00 p.m. – 6:00 p.m. Hosted by Texas Instruments, Inc.

Students, have you ever wondered what career opportunities exist in the industry and how you could use your technical skills and innovative talent? If so, you are invited to attend the ECTC Student Reception, where you will have the opportunity to talk to industry professionals about what helped them be successful in their first job search and reach their current positions. You will have the chance to enjoy good food and network with industry leaders and achievers. Don't miss the opportunity to interact with people that you might not have the chance to meet otherwise! Sponsored by Texas Instruments, Inc.

# **Exhibitor Reception**

Wednesday, May 27, 2020 • 5:30 p.m. – 6:30 p.m. All badged attendees are invited to attend a reception in the exhibition hall.

# 70th ECTC Gala Reception

**Thursday, May 28, 2020 • 6:30 p.m.** All badged attendees and their guests are invited to attend a reception hosted by the Gala Reception sponsors. Executive Committee General Chair Christopher Bower X Display Company, Inc. chris@xdisplay.com +1-919-522-3230

Vice General Chair Nancy Stoffel GE Research nstoffel1194@gmail.com +1-518-387-4529

Program Chair Rozalia Beica AT&S rbeica.semi@gmail.com

Assistant Program Chair Ibrahim Guven Virginia Commonwealth University iguven@vcu.edu +1-804-827-3652

Jr. Past General Chair Mark Poliks Binghamton University mpoliks@binghamton.edu +1-607-727-7104

Sr. Past General Chair Sam Karikalan Broadcom, Inc. sam.karikalan@broadcom.com +1-949-926-7296

Sponsorship Chair Wolfgang Sauter Marvell Semiconductor, Inc. wsauter2@gmail.com

Finance Chair Patrick Thompson Texas Instruments, Inc. patrick.thompson@ti.com +1-214-567-0660

Publications Chair Henning Braunisch Intel Corporation braunisch@ieee.org +1-480-552-0844

Publicity Chair Eric Perfecto eperfecto@gmail.com +1-845-894-4400

Treasurer Tom Reynolds T3 Group LLC treynolds@ieee.org +1-850-897-7323

Exhibits Chair Alan Huffman Micross Advanced Interconnect Technology alan.huffman@micross.com +1-919-248-9216

IT Coordinator Karlheinz Bock TU Dresden karlheinz.bock@tu-dresden.de +49-351-463-36345

Professional Development Course Chair Kitty Pearsall Boss Precision, Inc. kitty.pearsall@gmail.com +1-512-845-3287

Conference Management Lisa Renzi Ragar Renzi & Company, Inc. Irenzi@renziandco.com +1-703-863-2223

EPS Representative C. P. Wong Georgia Institute of Technology cp.wong@mse.gatech.edu +1-404-894-8391

#### Packaging Technologies

Chair Luke England GLOBALFOUNDRIES luke.england@globalfoundries.com +1-518-222-1860

Assistant Chair Markus Leitgeb AT&S

m.leitgeb@ats.net +43-676-8955-4087 Daniel Baldwin H.B. Fuller Company

Bora Baloglu Amkor Technology, Inc. lie Fu

Apple, Inc. Mike Gallagher DuPont Electronic and Imaging

Ning Ge Consultant Allyson Hartzell Veryst Engineering

Kuldip Johal Atotech

Beth Keser

Intel Corporation Young-Gon Kim Renesas Electronics America

Andrew Kim

Intel Corporation John Knickerbocker IBM Corporation

Steffen Kroehnert ESPAT Consulting, German

Albert Lan Applied Materials John H. Lau Unimicron Technology Corporation Jaesik Lee

Nvidia Dean Malta Micross Advanced Interconnect Technology

Luu Nguyen Psi Quantum

Deborah S. Patterson Harbor Electronics, Inc.

Raj Pendse Facebook FRL Subhash L. Shinde

Notre Dame University Joseph W. Soucy Draper Laboratory

Peng Su Juniper Networks Kuo-Chung Yee Taiwan Semiconductor Manufacturing

#### Company, Ltd. Applied Reliability

Chair Darvin R. Edwards Edwards Enterprise Consulting, LLC darvin.edwards1@gmail.com +1.972-571-7638

Assistant Chair Keith Newman AMD

keith.newman@amd.com +1-(408) 749-5566

Seung-Hyun Chae SK Hynix Tz-Cheng Chiu

Intel Corporation

National Cheng Kung University Deepak Goyal Vikas Gupta Texas Instruments, Inc. Sandy Klengel Fraunhofer Institute

Pilin Liu Intel Corporation Varughese Mathew

NXP Semiconductors Toni Mattila Aalto University

Donna M. Noctor Nokia

S. B. Park Binghamton University Lakshmi N. Ramanathan

Microsoft Corporation René Rongen

NXP Semiconductors

Scott Savage Medtronic Microelectronics Center Christian Schmidt

NVIDIA Corporation Jeffrey Suhling

Auburn University Pei-Haw Tsao

Taiwan Semiconductor Manufacturing Company, Ltd.

Dongji Xie NVIDIA Corporation

#### Assembly & Manufacturing Technology Chair

Jin Yang Intel Corporation jin1.yang@ieee.org +1-971-214-9041

Assistant Chair Christo Bojkov Qorvo cpb2016@sbcglobal.net +1-972-994-8229

Sai Ankireddi Maxim Integrated

Mark Gerber Advanced Semiconductor Engineering Inc. Habib Hichri Suss Microtech Photonic Systems, Inc. Paul Houston

Engent Li Jiang Texas Instruments

Chunho Kim

Medtronic Corporation Wei Koh

Pacrim Technology

Ming Li ASM Pacific Technology

Debendra Mallik Intel Corporation

Jae-Woong Nah IBM Corporation

Valerie Oberson IBM Canada, Ltd. Chandradip Patel

Schlumberger Technology Corporation Shichun Ou

Intersil, a Renesas Company Paul Tiner

Texas Instruments, Inc. Andy Tseng

JSR Micro

Jan Vardaman Techsearch International Yu Wang Sensata Technologies Shaw Fong Wong Intel Corporation Wei Xu Huawei Tonglong Zhang Nantong Fujitsu Microelectronics, Ltd.

# High-Speed, Wireless & Components

Chair Lianjun Liu NXP Semiconductor, Inc. Iianjun.liu@NXP.com +1-480-413-4022

Assistant Chair Yong-Kyu Yoon University of Florida ykyoon@ece.ufl.edu +1-352-392-598

Amit P. Agrawal Microsemi Corporation

Kemal Aygun Intel Corporation

Wendem Beyene Intel Corporation

Eric Beyne IMEC

Prem Chahal Michigan State University

Zhaoqing Chen IBM Corporation

Charles Nan-Cheng Chen Shanghai Jiao Tong University Craig Gaw

NXP Semiconductor

Abhilash Goyal Velodyne LIDAR, Inc.

Xiaoxiong (Kevin) Gu IBM Corporation

Rockwell Hsu Cisco Systems, Inc.

Lih-Tyng Hwang National Sun Yat-Sen University

Timothy G. Lenihan TechSearch International

Rajen M Murugan Texas Instruments, Inc.

Nanju Na Xilinx

Ivan Ndip Fraunhofer Institute for Reliability and Microintegration (IZM)

Dan Oh Samsung

P. Markondeya Raj Georgia Institute of Technology

Hideki Sasaki Renesas Electronics Corporation Li-Cheng Shen

Wistron NeWeb Corporation

Qualcomm Corporation

Manos M. Tentzeris Georgia Institute of Technology Maciej Wojnowski Infineon Technologies AG

Emerging Technologies Chair

Benson Chan Binghamton University chanb@binghamton.edu +1-607-777-4349

Georgia Institute of Technology

7

Assistant Chair

W. Hong Yeo

whyeo@gatech.edu

+1-404-385-5710

Isaac Robin Abothu Siemens Healthineers

Meriem Akin Volkswagen

Vasudeva P. Atluri Renavitas Technologies

Karlheinz Bock Technische Universitat Dresden

Vaidyanathan Chelakara Acacia Communications

Rabindra N. Das MIT Lincoln Labs

Dongming He Qualcomm Technologies, Inc.

Florian Herrault HRL Laboratories, LLC

Jae-Woong Jeong KAIST

TengFei liang University of Central Florida Jong-Hoon Kim

Washington State University Vancouver Ahyeon Koh Binghamton University

Ramakrishna Kotlanka Analog Devices

Santosh Kudtarkar Analog Devices

Kevin J. Lee Qorvo Corporation

Zhuo Li Fudan University Chukwudi Okoro Corning

C. S. Premachandran GLOBALFOUNDRIES

Jintang Shang Southeast University

Rohit Sharma IIT Roda Nancy Stoffel

GE Research Liu Yang

**IBM** Corporation

Intel Corporation

**IBM** Corporation

Chair Dingyou Zhang Broadcom Inc

Nanyang Technological University tancs@alum.mit.edu +65-67905636

Thibault Buisson Yole Développement

Jian Cai Tsinghua University

Zhang Chaoqi Qualcomm Inc

William Chen Advanced Semiconductor Engineering, Inc.

University of Sherbrooke Rajen Dias

Amkor Technology, Inc. Bernd Ebersberger Infineon Technologies Takafumi Fukushima

Tohoku University

Tom Gregorich Zeiss Semiconductor Manufacturing Technology Chung C. Key Advanced Packaging Division, Corp. R&D, SPIL Ltd. Seung Yeop Kook GLOBALFOUNDRIES Li Li Cisco Systems, Inc. Changqing Liu Loughborough University Wei-Chung Lo ITRI Nathan Lower Collins Aerospace James Lu Rensselaer Polytechnic Institute Peter Ramm Fraunhofer EMFT Katsuyuki Sakuma IBM Corporation Lei Shan **IBM** Corporation Ho-Young Son SK Hynix Jean-Charles Souriau CEA Leti Xin Yan Intel Matthew Yao GE Aviation Materials & Processing Chair Tania Braun Fraunhofer IZM tanja.braun@izm.fraunhofer.de +46-304-6403244 Assistant Chair Kimberly Yess Brewer Science kyess@brewerscience.com +1-573-201-8669 Yu-Hua Chen Unimicron Qianwen Chen IBM Research Jae Kyo Cho GLOBALFOUNDRIES Bing Dang IBM Research Yung-Yu Hsu Apple, Inc. Lewis Huang Seniu Electronic C. Robert Kao National Taiwan University Alvin Lee Brewer Science Yi (Grace) Li Intel Corporation 7ivin I in Intel Corporation Yan Liu

Medtronic Inc. USA Mikel Miller Apple, Inc. Praveen Pandojirao-S Mark Poliks Dwayne Shirley

Bo Song HP Inc. Yoichi Taira Keio University Lejun Wang Analog Devices Frank Wei Disco Japan Lingyun (Lucy) Wei Dupont Myung Jin Yim Apple, Inc. Hongbin Yu Arizona State University Zhangming Zhou Qualcomm Thermal/Mechanical Simulation & Characterization Chair Przemyslaw Gromala Robert Bosch GmbH Przemyslawjakub.gromala@de.bosch.com +49-162-8514983 Assistant Chair Ning Ye Western Digital ning.ye@wdc.com +1-408-801-1278 Christopher J. Bailey University of Greenwich Kuo-Ning Chiang National Tsinghua University Xuejun Fan Lamar University Nancy Iwamoto Honeywell Performance Materials and Technologies Pradeep Lall Auburn University Chang-Chun Lee National Tsing hua University (NTHU) Sheng Liu Wuhan University Yong Liu ON Semiconductor Erdogan Madenci University of Arizona Tony Mak Wentworth Institute of Technology Karsten Meier Technische Universität Dresden Erkan Oterkus University of Strathclyde Suresh K. Sitaraman Georgia Institute of Technology Wei Wang Qualcomm Technologies, Inc. G. Q. (Kouchi) Zhang Delft University of Technology (TUD) Tieyu Zheng Microsoft Corporation Jiantao Zheng Hisilicon Photonics Chair Z. Rena Huang Rensselaer Polytechnic Institute zrhuang@ecse.rpi.edu +1-518-276-6086

Assistant Chair Harry G. Kellzi Micropac Industries harrykellzi@micropac.com +1-972-272-371

Mark Beranek Naval Air Systems Command Stephane Bernabe CEA Leti

Fuad Doany IBM Research

Gordon Elger Technische Hochschule Ingolstadt Takaaki Ishigure

Keio University

Ajey Jacob GLOBALFOUNDRIES

Soon Jang ficonTEC, USA

Richard Pitwon Resolute Photonics Ltd Alex Rosiewicz

A2F Partners Henning Schroeder

Fraunhofer IZM Andrew Shapiro

IPI

Masato Shishikura Oclaro Japan

Masao Tokunari IBM Corporation

Shogo Ura Kyoto Institute of Technology

Stefan Weiss II-VI Laser Enterprise GmbH Feng Yu Huawei Technologies Japan

Thomas Zahner OSRAM Opto Semiconductors GmbH

Ping Zhou LDX Optronics, Inc.

**Interactive Presentations** Chai

Pavel Roy Paladhi IBM Corporation rpaladhi01@gmail.com +1-512-286-9677-

Assistant Chair Michael Mayer University of Waterloo mmayer@uwaterloo.ca +1-519-888-4024

Rao Bonda Amkor Technology, Inc.

Mark Eblen Kyocera International SC

Ibrahim Guven Virginia Commonwealth University

Alan Huffman Micross Advanced Interconnect Technology

Jeffrey Lee iST-Integrated Service Technology Inc.

Nam Pham **IBM** Corporation

Mark Poliks Binghamton University

Patrick Thompson Texas Instruments, Inc.

Kristina Young-Fisher GLOBALFOUNDRIES

#### **Professional Development Courses** Chair Kitty Pearsall

Boss Precision, Inc. kitty.pearsall@gmail.com +1-512-845-3287

Co-Chair Jeffrey Suhling Auburn University jsuhling@auburn.edu +1-334-844-3332

Deepak Goyal Intel Corporation

Lakshmi N. Ramanathan Microsoft Corporation

limin Yao

# Hongqing Zhang

# Interconnections

# dingyouzhang.brcm@gmail.com Assistant Chair Chuan Seng Tan

# David Danovitch

# Johnson & Johnson Binghamton University

# Inphi

Ivan Shubin **RAM** Photonics

# PROFESSIONAL DEVELOPMENT COURSES

# Tuesday, May 26, 2020

Kitty Pearsall, Chair Boss Precision, Inc. kitty.pearsall@gmail.com +1-512-845-3287

Jeff Suhling, Assistant Chair Auburn University jsuhling@auburn.edu +1-334-844-3332

# MORNING COURSES 8:00 a.m. - 12:00 Noon

#### 1. ACHIEVING HIGH RELIABILITY OF LEAD-FREE SOLDER JOINTS --MATERIALS CONSIDERATIONS Course Leader: Ning-Cheng Lee – Indium Corporation

#### **Course Objective:**

This course covers the detailed material considerations required for achieving high reliability for lead-free solder joints. The reliability discussed includes joint mechanical properties, development of type and extent of intermetallic compounds (IMC) under a variety of material combinations and aging conditions, and how those IMCs affect the reliability. The failure modes, thermal cycling reliability, fragility of solder joints as a function of material combination, thermal history, and stress history will be addressed in details. The selection of novel alloys with reduced fragility will be presented. Crucial parameters for high reliability solder alloy for automotive industry will be presented. Electromigration and tin whisker growth will also be discussed. The emphasis of this course is placed on the understanding of how the various factors contribute to the failure modes, and how the selection of proper solder alloys and surface finishes for achieving high reliability are key.

#### **Course Outline:**

- 1. Main Stream Lead-free Soldering Practice

- 2. Surface Finishes Issues

- 3. Mechanical Properties

- 4. Intermetallic Compounds

- 5. Failure Modes

- 6. Reliability Thermal Cycle

- 7. Reliability Fragility

- 8. Reliability Rigidity & Ductility

- 9. Reliability Electromigration

- 10. Reliability Tin Whisker

#### Who Should Attend:

Directors, managers, design engineers, process engineers, and reliability engineers who care about achieving high reliability lead-free solder joints and would like to know how to achieve it should take this course.

# **IMPORTANT NOTICE**

It is extremely important to register in advance to prevent delays at door registration. Course sizes are limited.

# 2. INTRODUCTION TO FAN-OUT WAFER LEVEL PACKAGING

# Course Leader: Beth Keser – Intel Corporation

# Course Objective:

Fan-out wafer level packaging (FO-WLP) technologies have been developed across the industry over the past 15 years and have been in high volume manufacturing for over 10 years. FO-WLP has matured enough that it has come to a crossroads where it has the potential to change the electronic packaging industry by eliminating wire bond and bump interconnections, substrates, leadframes, the traditional flip chip or wire bond chip attach and underfill assembly technologies across multiple applications. This course will cover the advantages of FO-WLP, potential application spaces, package structures available in the industry, process flows, material challenges, design rule roadmap, reliability, and benchmarking.

#### **Course Outline:**

- 1. Current Challenges in Packaging

- 2. Definition and Advantages

- 3. Applications

- 4. Package Structures

- 5. Process

- 6. Material Challenges

- 7. Equipment Challenges

- 8. Design Rule Roadmap

- 9. Reliability

- 10. Benchmarking

# Who Should Attend:

Engineers and managers responsible for advanced packaging development, package characterization, package quality, package reliability, and package design should attend this course. Suppliers who are interested in supporting the materials and equipment supply chain should also attend. Both newcomers and experienced practitioners are welcome.

#### 3. FUNDAMENTALS OF GLASS TECHNOLOGY AND APPLICATIONS FOR ADVANCED SEMICONDUCTOR PACKAGING

Course Leaders: Prakash Gajendran and Joseph Canale – Corning, Inc.

#### **Course Objective:**

This course is intended to guide technologists toward a deeper understanding of how to leverage engineered glass as a material for advanced IC packaging applications. Following a review of the fundamental principles of glass structure, composition, and properties, we will discuss the unique attributes that make glass an enabling material: including strength and reliability, chemical durability, thermal behavior, associated thermal relaxation behavior, and electrical properties. In addition, we will review the "glass toolkit" as a platform alternative for semiconductor packaging development including various manufacturing (glass melting and forming) approaches, the diversity of compositional options, and a survey of glass processing approaches that can be adapted from adjacent glass technology spaces to advanced semiconductor packaging. Finally, a series of case studies will illustrate how glass is contributing to emerging technologies in the microelectronics' space and explore current and potential applications in advanced semiconductor packaging, consumer electronics, and internet of things (IoT) applications. Examples include the role of glass as a carrier

for temporary bonding, integrated glass wafers for optical sensors and augmented reality, key components in RF communications, as well as glass interposers for 2.5D and 3D packaging.

#### **Course Outline:**

- 1. Fundamentals of Glass

- What is Glass?

- Overview of Glass Attributes

- 2. Versatility of Glass

- Glass Composition Review

- Melting and Forming Process

- Overview of Major Forming Processes

- Secondary Processes

- Options for Enhanced Properties

- 3. Major Applications and Markets

- Wafer-Level Optics

- Semiconductor

- Case Studies

### Who Should Attend:

Engineers, technical managers, scientists, buyers, and managers involved in materials, research and development, as well as advanced semiconductor packaging should attend. We welcome individuals or companies with little or no experience in using glass.

#### 4. POST-MOORE'S LAW AND QUANTUM ELECTRONICS (PMQE) Course Leader: Rao Tummala – Georgia Institute of Technology

#### **Course Objective:**

Moore's law has been the driving engine for science, technology, manufacturing, hardware, software, systems, and applications, contributing to the prosperity of thousands of individuals, hundreds of corporations, and dozens of countries. As Moore's Law begins to come to an end, not only for fundamental reasons but also for computing performance, power, cost, and investments, it is becoming clear that a different vision for electronics systems must emerge. So, while transistor integration to a 20 billion-transistor-chip on individual ICs so far was the basis of Moore's Law for ICs, this can be extended in 2.5D and 3D by means of new paradigms in electronic and optoelectronic interconnections, in the short term. This is referred to as Moore's Law for Packaging or interconnections. Just like Moore's Law has both the doubling of transistors and simultaneous cost reduction from node to node, every 18-24 months, Moore's Law for Packaging can do the same.

Interconnections have been driven by computing systems and within computing systems, between logic and memory, consistent with Von Neumann's architecture. The new era of artificial intelligence mimicking the human brain, with several orders of magnitude of better computer performance than with the current electronics, is yet another reason for the end of Moore's Law. The human brain is the ultimate system packaging for the highest performance in the smallest size with the lowest power. A typical human brain has about 90 billion nerve cells interconnected by trillions of synapses providing trillions of pathways for the brain to process the information along with petabyte memory. Thus the human brain is the new standard in packaging density and computing performance-power efficiency. This is more than the current 3D electronic architectures. There is no such electronics equivalent. Therefore the new PMQE law must duplicate this architecture. This tutorial describes a vision for post-Moore's Law and Quantum Electronics (PMQE) from current era of

Moore's Law for ICs to the next era of electronic and photonic interconnections, and eventually to quantum electronics and computing. All large corporations such as Google, IBM, Microsoft, Intel and advanced countries such as the U.S., Europe, Japan, and China have targeted quantum electronics as the next Moore's Law. Quantum electronics consist of Quantum devices with superconducting interconnections that operate at absolute zero degrees Kelvin. Unlike current computing, which operates with binary 0 or 1, quantum operates with both simultaneously. This is referred to as Qubits. This leads to an exponential increase in computing power, as demonstrated by IBM and Google. Currently Qubits are only at about 50. Post-Moore's Law electronics is highly interdisciplinary, requiring a team of scientists and engineers to work together from electrical, mechanical, thermal, optical, bio and nanomaterials, and chemical process disciplines. The PMQE provides a new opportunity for the electronics industry to continue, not on Moore's Law path, but on a computing roadmap.

#### **Course Outline:**

- 1. Current Approach to Devices and Systems

- 2. Moore's Law for ICs, Its Evolution and Its Future

- 3. Reasons for Moore's Law Coming to an End

- 4. What Will Replace Moore's Law?

- 5. Moore's Law for Electronic and Photonic Packaging as the 2nd Moore's Law

- 6. Quantum Electronics for the Next Computing Wave

#### Who Should Attend:

R&D executives as well as senior technical and marketing managers involved in all aspects of electronics R&D, supply-chain for ICs, packages and systems manufacturing, marketing, investments and users who deal with strategic directions for their company.

#### 5. NANO MATERIALS AND POLYMER COMPOSITES FOR ELECTRONIC PACKAGING

#### Course Leaders: C. P. Wong – Georgia Institute of Technology; Daniel Lu – Henkel Corporation

#### **Course Objective:**

Nano materials and polymer composites are widely used in electronic and photonic packaging as adhesives, encapsulants, thermal interface materials, insulators, dielectrics, molding compounds, and conducting elements for interconnects. These materials also play a critical role in the recent advances of low-cost, high performance encapsulants for flip-chip, chip scale packaging (CSP), system in a package (SIP) and 3D packaging, conductive adhesives (both ICA and ACA), embedded passives (high K polymer composites), and nano particles and nano-functional materials such as CNTs (some with graphenes). It is imperative that both material suppliers, formulators and their users have a thorough understanding of polymeric materials and the recent advances on nano materials and their importance in the advances of the electronic packaging and interconnect technologies.

#### Course Outline:

- 1. Introduction to Nanotechnology

- 2. Nano Solder

- 3. Carbon Nanotube

- 4. Nano Materials for Wafer Level Packaging

- 5. Super Hydrophobic Surface

- 6. Surface Functionalization

- 7. Functionalized Graphene for Energy Storage and Electrocatalysis

- 8. Electrically Conductive Adhesives

- 9. Conductive Nano Composites

- 10. Conductive Nano-ink

- 11. Transparent Nanocomposite

### Who Should Attend:

Students, researchers, engineers, scientists and managers who are involved in research and development, designing, processing and manufacturing of microelectronic and optoelectronic components and packages, and suppliers and developers of materials for semiconductor and electronic packaging should attend.

#### 6. FUNDAMENTALS OF RF DESIGN AND FABRICATION PROCESSES OF FAN-OUT WAFER/PANEL LEVEL PACKAGES AND INTERPOSERS

Course Leaders: Ivan Ndip and Markus Wöhrmann – Fraunhofer IZM

# **Course Objective:**

Due to their myriad of advantages in systemintegration, fan-out wafer/panel level packages (FO WLPs/PLPs) and interposers will play a key role in the development of emerging electronic systems, especially for 5G applications. The fabrication processes and RF performance of these advanced packages, especially their multi-layered redistribution layers (RDLs), required for the interconnection of the chips and other system components, will contribute significantly to the cost and performance of the entire system. The objective of this course is to provide and illustrate the fundamentals of the fabrication processes and RF design of FO WLPs/ PLPs and interposers, including their multi-layered RDLs.

An overview of different types of wafer-level packages, fan-out technologies and interposers will first be given. This will be followed by a presentation of new fan-out-packaging and interposer-based concepts for emerging applications (e.g., 5G) as well as a thorough discussion of the materials and fundamentals of the fabrication processes of FO-WLPs/PLPs, multilayered RDLs and glass/silicon interposers. The basics of efficient RF design and measurement of the fundamental building blocks of FO-WLPs/PLPs and glass/silicon interposers will be given for frequencies right up in the millimeter-wave range. Finally, examples of these advanced packages designed and fabricated at Fraunhofer IZM will be discussed.

#### **Course Outline:**

- 1. Overview of Different Types of Wafer-Level Packages, Fan-Out Technologies and Interposers

- Requirements of 5G Packaging

New Fan-Out Packaging and Interposer-Based

- Concepts for 5G Applications 4. Materials and Fabrication Processes: FO-WLPs/

- Materials and Fabrication Processes: FO-VVLPs/ PLPs, Multi-layered RDLs, and Silicon/Glass Interposers

- 5. Fundamentals of RF Design and Measurement: FO-WLPs/PLPs, RDLs, and Silicon/Glass Interposers

- 6. Comparison of RF Performance of Interconnects in FO-WLPs/PLPs and Silicon/ Glass Interposers

- 7. Examples of Advanced Packages Designed and Fabricated at Fraunhofer IZM

#### Who Should Attend:

Engineers, scientists, researchers, designers, managers and graduate students interested in the fundamentals of electronic packaging as well as those involved in the process of electrical design, layout, processing, fabrication and/or system-integration of electronic packages for emerging applications (e.g., 5G) should attend.

#### 7. ELIMINATING PACKAGE FAILURE MECHANISMS FOR IMPROVED RELIABILITY

#### Course Leader: Darvin Edwards – Edwards Enterprises

#### **Course Objective:**

Past and present reliability failure mechanisms that plague semiconductor packages will be explored. Major reliability challenges and failure mechanisms are detailed in critical emerging and high-volume package technologies such as TSVs, FOWLPs, WLCSPs, FC-BGAs, plastic leaded, and no lead packages. Topics studied include reliability of TSVchip interactions, micro bump mechanical reliability, electromigration performance, stress induced ILD damage under bumps and wire bonds, Cu vs. Au wire bond reliability comparisons, complications associated with package delamination, solder joint reliability, system level issues such as drop and bend reliability, and the impact of aging on reliability performance. For each failure mode, the resultant failure mechanisms and failure analysis techniques required to verify the mechanisms will be summarized. Fundamental failure analysis fault isolation techniques are described. This solutions-focused course concentrates on key process parameters, design techniques and material selections that can eliminate failures and improve reliability, ensuring participants can design-in reliability and design-out failures for faster time to market. Characterization and implementation of test structures and design guidelines that enable reliable first pass products will be described and encouraged. A methodology for early detection of chip/package interaction (CPI) reliability risks will be described.

#### **Course Outline:**

- 1. Introduction to Package Reliability

- 2. Failure Modes vs. Failure Mechanisms

- 3. Failure Analysis Techniques and Fault Isolation

- 4. FC-BGA Package Failure Mechanisms

- 5. Molded and Leaded Package Failure Mechanisms

- 6. WLCSPs Package Failure Mechanisms

- 7. Embedded Die & Fan-Out WLP Failure Mechanisms

- 8. TSV Failure Mechanisms

- 9. Materials, Modeling, Design Rules, and Reliability

- 10. Common Test Structures for Failure Mechanism Identification

- 11. Qualification by Similarity (QBS)

- 12. Summary

#### Who Should Attend:

This class is for all who work with IC packaging, package reliability, package development, package design, and package processing where a working knowledge of package failure mechanisms is beneficial. Beginning engineers and those skilled in the art will benefit from the holistic failure mechanism descriptions and the provided proven solutions

#### 8. CHARACTERIZATION OF ADVANCED EMCS FOR FO-WLP, HETEROGENEOUS INTEGRATION, AND AUTOMOTIVE ELECTRONICS

Course Leaders: Przemyslaw Gromala – Robert Bosch GmbH; Bongtae Han – University of Maryland

### **Course Objective:**

Epoxy-based molding compounds (EMCs) are widely used in the semiconductor industry as one of the most important encapsulating materials. For the advanced packaging technologies, in particular, FO-WLP technologies and heterogeneous integrations, EMCs play a more significant role than for the conventional plastically-encapsulated packages because of thin profiles and complex process conditions required for the advanced packaging technologies. In the automotive industry where demand for more advanced packaging technologies increases rapidly for autonomous and connected cars, EMCs are often used to protect not only individual IC components but also entire electronic control units (ECUs), or power modules.

The stress caused by the mismatch of the coefficient of thermal expansion (CTE) between EMCs and adjacent materials is one of the major causes of reliability problems (e.g., excessive warpage, delamination, BRL, etc.). During assembly or even operating conditions, EMCs are subjected to temperatures beyond the glass transition temperature. Around the glass transition temperature, EMCs exhibit significant volumetric and isochoric viscosity, which leads to nonlinear viscoelastic behavior. In contrast, at low temperatures, EMCs show linear viscoelastic behavior. This complex material characteristic in the full temperature range of interest renders the design of electronic devices a nontrivial task. The mechanical behavior of EMCs has to be understood clearly to offer predictive simulation strategies, which has become an integral part of product development process.

This training will address details of such strategies, summarizes the required material characterization procedure, and closes with some representative examples.

# **Course Outline:**

- 1. Introduction

- 2. Selection of the Material (Preliminary Qualitative Analysis)

- 3. Material Characterization

- 4. Cure Kinetics

- 5. Curing Shrinkage

- 6. Coefficient of Thermal Expansion

- 7. Linear Viscoelastic Properties

- 8. Master Curve and Shift Factor of Young's Modulus

- 9. Master Curve and Shift Factor of Bulk Modulus

- 10. Viscoelastic Behavior in the Non-linear Domain

11. Summary

#### Who Should Attend:

Engineers and technical managers who are already involved in the material characterization and modelling, numerical modelling, process engineers and PhD students who need fundamental understanding or broad overview should attend.

#### 9. RELIABLE INTEGRATED THERMAL PACKAGING FOR POWER ELECTRONICS

# Course Leader: Patrick McCluskey – University of Maryland

#### Course Objective:

Power electronics are becoming ubiquitous in engineered systems as they replace traditional ways to control the generation, distribution, and use of energy. They are used in products as diverse as home appliances, cell phone towers, aircraft, wind turbines, radar systems, smart grids, and data centers. This widespread incorporation has resulted in significant improvements in efficiency over previous technologies, but it also has made it essential that the reliability of power electronics be characterized and enhanced. Recently, increased power levels, made possible by new compound semiconductor materials, combined with increased packaging density have led to higher heat densities in power electronic systems, especially inside the switching module, making thermal management more critical to performance and reliability of power electronics.

This course will emphasize approaches to integrated thermal packaging that address performance limits and reliability concerns associated with increased power levels and power density. Following a quick review of active heat transfer techniques, along with prognostic health management, this short course will present the latest developments in the materials (e.g. organic, flexible), packaging, assembly, and thermal management of power electronic modules, MEMS, and systems and in the techniques for their reliability assessment.

#### **Course Outline:**

- 1. Motivation for Integrated Thermal Packaging for Reliable Power Electronic Systems and Heterogeneous Integration

- Simulation and Assessment of Active Thermal Management Techniques: Air; Single Phase Liquid; Two Phase; Heat Pipes; and, Thermoelectric

- 3. Application of Thermal Management Techniques to Commercial Power Systems

- 4. Durability Assessment: Failure Modeling; Simulation; Testing; and, Health Monitoring

- 5. Reliability and Thermal Packaging of Active Devices: Si; SiC; GaN; and, Interconnects

- 6. Reliability and Thermal Packaging of Switching Modules, including organic encapsulants

- 7. Reliability in Rigid Assembly Packaging: PCBs; Solders; and, Passives

- 8. Flexible Materials, Packaging, and Thermal Management: Flex circuit and OLED

- 9. Reliability of Additive Manufactured and Embedded Power Electronics

#### Who Should Attend:

This course is intended for engineers and managers who want to learn more about the thermal limitations and reliability concerns involved in the heterogeneous integration and packaging of power electronic devices and systems.

# AFTERNOON COURSES 1:15 p.m. – 5:15 p.m.

10. FLIP CHIP TECHNOLOGIES Course Leaders: Eric Perfecto – IBM Corporation and Shengmin Wen – Synaptics Inc.

#### **Course Objective:**

This course will cover the fundamentals of all aspects of flip chip assembly technology, including wafer bumping, substrate selection, solder joint formation in various assembly processes, underfill, and reliability evaluation. The course is divided into two major sections.

The first section focuses on the key steps of flip chip assembly processes and their respective equipment that are involved. Plenty of examples are presented to show the versatile flip-chip applications to single-die, monolithic multi-die, multi-level multi-die flip chip integration, as well as multi-form interconnection such as wire bond / flip chip mixed integration - the SiP integration. At the same time, major flip chip assembly packages are discussed, such as BGA packages, CSP packages, wafer-level fan-in and fan-out packages, chip-on-chip packages, chip-on-wafer packages, and 2.5D/3D flip chip packages, together with actual industrial leading application cases. In-depth discussions include chip package interaction (CPI), package warpage control, yield detractors for flip-chip assembly, substrate technologies, failure modes and root cause analysis, reliability tests, and the important roles of electrical and mechanical simulation, Si die floor plan optimization and its consequence on packaging, among others. Students will understand the versatility of flip chip technologies and learn a range of criteria that they can apply to their daily work needs. This section also provides the trend in the flip chip assembly technologies.

The second section dives into the depth of the fundamental aspect of flip chip technology. It will detail the various interconnect technologies that are used in today's flip chip assembly, i.e., lead-free solder bumping, highly customized Cu-Pillar bumping, intermetallic and Cu-to-Cu joining. It will discuss the various under-bump metallurgy (UBM) fabrication methods (electroplating, electroless plating and sputtering) and solder depositions methods (electroplating, ball drop, IMS, and solder screening). The course will cover the various failure modes related to bumping, such as barrier consumption, Kirkendall void formation, non-wets, BEOL dielectric cracking, electromigration, etc.

#### **Course Outline:**

- 1. Introduction to Flip-Chip Technologies

- 2. Flip Chip Technologies: Mass Reflow Process

- 3. Flip Chip Technologies: Thermal Compression

- 4. Substrate Technologies, Underfill, Package Warpage Control, and Yield

- 5. Flip Chip Reliability Assessment, Failure Modes, Examples, and Modeling

- 6. Flip Chip Si Package Co-Design and Chip-Package Interaction

- 7. Flip Chip New Trends: Wafer Level CSP; Waver Lever Fan-Out; and, Panel Level Packaging

- 8. Bumping Ground Rules

- 9. Flip Chip Under-Bump Metal and Intermetallic

- 10. Flip Chip Solder Deposition Processes

- 11. Cu Pillar Technology

- 12. Flip Chip Solder Selection and Characterization

- 13. Flip Chip Electromigration

- 14. Non-Solder Interconnects

- 15. Review and Package Selection Exercise

# Who Should Attend:

The goal of this course is to provide the students with a list of options to apply to their particular flip chip assembly applications so that a reliable, innovative, better time to market, and more costeffective solution can be achieved. Students are encouraged to bring topics and technical issues from their past, present and future job function for group discussions. A group exercise at the end of the class is planned to serve as a capstone project, making sure that the students can walk away with an in-depth understanding of the technology, and are ready to apply and meet their real-world packaging needs.

# **11. WAFER-LEVEL CHIP-SCALE** PACKAGING (WCSP) FUNDAMENTALS Course Leader: Patrick Thompson – Texas Instruments. Inc.

# **Course Objective:**

This course will provide an overview of the Wafer Level-Chip Scale Packaging (WLCSP) technology. The market drivers, end applications, benefits, and challenges facing industry-wide adoption will be discussed. Typical WLCSP configurations (bumpon-pad, bump-on-polymer, fan-in, and fan-out) will be discussed in terms of their construction, manufacturing processes, materials and equipment, and electrical and thermal performance, together with package and board level reliability. Extensions to higher pin count packages and other arenas such as RF sensors and MEMS will be reviewed. Future trends covered will include enhanced lead-free solder balls, large die size, wafer level underfill, thin and ultra-thin WLCSP, RDL (redistribution layer), stacked WLCSP, MCM in "reconstituted wafers," embedded components, and applications to large format (panel) processing. Since the technology marks the convergence of fab, assembly, and test, discussion will address questions on the industrial supply chain such as: Does it fit best with front-end or backend processing? Are the current standards for design rules, outline, reliability, and equipment applicable? What are the challenges for memory and other complex devices such as ASICs and microprocessors?

# **Course Outline:**

- 1. WL-CSP definition

- 2. Trends, Categories, Examples, Challenges, Supply Chain

- 3. Historical Overview, Package Highlights, Assembly Flow

- 4. Processing and Reliability: Flex, Temperature Cycling, Drop, Electromigration

- 5. Fan-Out Technologies

- 6. Embedded Technologies

- 7. Conclusions

#### Who Should Attend:

The course will be useful to the following groups of engineers: newcomers to the field who would like to obtain a general overview of WLCSP; R&D practitioners who would like to learn new methods for solving CSP problems; and, those considering WLCSP as a potential alternative for their packaging solutions.

### **12. ADDITIVE FLEXIBLE HYBRID ELECTRONICS – MANUFACTURING** AND RELIABILITY

#### Course Leader: Pradeep Lall – Auburn University

### **Course Description:**

In this course, manufacture, design, assembly, and accelerated testing of additively-printed flexible hybrid electronics for applications in some of the emerging areas will be covered. Manufacturing processes for additive-fabrication of flexible hybrid electronics will be discussed. Flexible hybrid electronics opens the possibilities for the development of stretchable, bendable, foldable form-factors in electronics applications, which have not been possible with the use of rigid electronics technologies. Flexible electronics may be subjected to strain magnitudes in the neighborhood of 50-150 percent during normal operation. The integration processes and semiconductor packaging architectures for flexible hybrid electronics may differ immensely in comparison with those used for rigid electronics. The manufacture of thin electronic architectures requires the integration of thin-chips, flexible encapsulation, compliant interconnects, and stretchable inks for metallization traces. A number of additive manufacturing processes for the fabrication and assembly of flexible hybrid electronics have become tractable. Processes for handling, pick-and-place operations of thin silicon and compliant interposers through interconnection processes such as reflow requires an understanding of the deformation and warpage processes for development of robust process parameters which will allow for acceptable levels of yields in high-volume manufacture. Modeling of operational stresses in flexible electronics requires the material behavior knowledge under loads including: constant exposure to human body temperature, saliva, sweat, ambient temperature, humidity, dust, wear, and abrasion. The strains imposed on flexible stretchable electronics may far exceed those experienced in rigid electronics requiring the consideration of finite-strain formulation in development of predictive models. The failure mechanisms, failure modes, acceleration factors in flexible electronics under operational loads of stretch, bend, fold, and loads resulting from human body proximity are significantly different than rigid electronics. The testing, qualification and quality assurance protocols to meaningfully inform manufacturing processes and ensure reliability and survivability under exposure to sustained harsh environmental operating conditions, may differ in flexible electronics as well. A number of product areas for the application of flexible electronics are tractable in the near-term including Internet-of-Things (IoT), medical wearable electronics, textile woven electronics, robotics, communications, asset monitoring, and automotive electronics.

#### **Course Outline:**

- 1. Additive Technologies in Flexible Electronics

- 2. Laser-Direct Sintering

- 4. Aerosol-Jet Printing

- 5. Ink-Jet Printing

- 6. Screen-Printing and Gravure Printing

- 7. Ultra-Thin Chips

- 8. Die-Attach Materials for Flexible Semiconductor Packaging

- 9. Compliant Interconnects

- 10. Flexible Encapsulation Materials

- 11. Dielectric Materials for Large-Area Flexible Flectronics

- 12. Flexible Substrates

- 13. Stretchable Inks for Printed Traces

- 14. Pick-and-Place and Material Handling Processes for Thin Chips

- 15. Reflow and Printing Processes

- 16. Accelerated Testing Protocols

#### Who Should Attend:

The targeted audience includes scientists, engineers, and managers considering the use of additively-printed flexible electronics or considering moving from rigid electronics to flexible electronics, as well as reliability, product or applications engineers who need a deeper understanding of additively-printed flexible electronics: the advantages; limitations; and, failure mechanisms.

#### **13. FAN-OUT WAFER/PANEL** LEVEL PACKAGING AND 3D IC HETEROGENEOUS INTEGRATIONS Course Leader: John Lau – Unimicron Technology Corporation

### **Course Objective:**

Recent advances in fan-out wafer/panel level packaging (TSMC's InFO-WLP and Fraunhofer IZM's FO-PLP), 3D IC packaging (TSMC's InFO\_PoP vs. Samsung's ePoP), 3D IC integration (Hynix/Samsung's HBM for AMD/NVIDIA's GPU vs. Micron's HMC for Intel's Knights Landing CPU), 2.5D IC Integration (TSV-less interconnects and interposers), embedded 3D hybrid integration, 3D CIS/IC integration, and 3D MEMS/IC integration will be discussed in this presentation. Emphasis is placed on various FO-WLP formation methods such as chip-first with die-up, chip-first with die-down, and chip-last (RDL-first). Since RDLs (redistribution layers) play an integral part of FO-WLP, various RDL fabrication methods such as Cu damascene, polymer, and PCB will be discussed. A few notes and recommendations on wafer vs. panel, dielectric materials, and molding materials will be provided. Also, TSV-less interposers such as those given by Xilinx/SPIL, Amkor, SPIL/Xilinx, ASE, MediaTek, Intel, ITRI, Shinko, Cisco/eSilicon, Sony's TSV-less CIS, and Samsung/Hynix (HBM3) will also be discussed. Furthermore, new trends in semiconductor packaging will be presented.

# **Course Outline:**

- Formation of FOWLP: (a) Chip-First (Die Face-Down), (b) Chip-First (Die Face-Up), and (c) Chip-Last (or RDL-First)

- 2. Fabrication of Redistribution Layers (RDLs): (a) Polymer and ECD Cu + Etching, (b) PECVD and Cu Damascene + CMP, (c) Hybrid RDLs, and (d) ABF/LDI and PCB Cu-plating + Etching

- 3. Warpages: (a) Warpage Types and (b) Allowable of Warpages

- 4. Reliability of FOWLP: (a) Thermal-Cycling Test, (b) Thermal-Cycling Simulations, (c) Drop Test, and (d) Drop Simulations

# 3. In-Mold Labeling

- 5. TSMC InFO: (a) InFO-PoP, and (b) InFO\_AiP/ RF-Chip Driven by 5G

- 6. Samsung PLP: (a) PoP for Smart Watches and (b) SiP SbS for Smartphones

- 7. Formation of FOPLP: (a) PCB + SAP, (b) PCB + LDI, (c) PCB + TFT-LCD, and (d) PCB/ABF/ SAP + LDI

- 8. Wafer vs. Panel: (a) Application Ranges of FOWLP and FOPLP, and (b) Critical Issues of FOPLP

- Trends in FOWLP and FOPLP

- 10. System-on-Chip (SoC)

- 11. Heterogeneous Integrations or SiPs

- 12. Heterogeneous Integrations vs. SoC

- 13. Heterogeneous Integrations on Organic Substrates

- 14. Heterogeneous Integrations on Silicon Substrates (TSV-Interposers)

- 15. Heterogeneous Integrations on Silicon Substrates (TSV-Less Interposers)

- 16. Heterogeneous Integrations on Fan-Out RDL Substrates: STATSChipPac's FOFCeWLB, ASE's FOCoS, MediaTek's FO-RDLs, Samsung's Si-Less RDL Interposer, and TSMC's InFO\_oS, and InFO\_MS

- 17. Heterogeneous Integration of (a) PoP, (b) Memory Stacks, (c) Chip-to-Chip Stacks, (d) CIS and Logic Chip, (e) LED and TSV-Interposers, (f) MEMS and Logic Chip, and (g) VESCL and PD

- 18. Trends in Heterogeneous Integrations

#### Who Should Attend:

If you are involved with any aspect of the electronics/optoelectronic industry, you should attend this course. Each participant will receive more than 200 pages of handout materials from the lecturer's books and the papers published by others.

# **14. POLYMERS IN WAFER LEVEL** PACKAGING

#### Course Leader: Jeffrey Gotro -InnoCentrix, LLC

#### **Course Objective:**

The course will provide an overview of polymers used in wafer level packaging and the important structure-property-process-performance relationships for polymers used in wafer level packaging. The main learning objectives will be: 1) understand the types of polymers used in wafer level packages, including underfills (pre-applied and wafer applied), mold compounds, and substrate materials; 2) gain insights on how polymers are used in Fan Out Wafer Level Packaging, specifically mold compounds and polymer redistribution layers (RDL); and, 3) learn the key polymer and processes challenges in Fan Out Wafer Level Packaging including panel level processing. We will cover in more depth the chemistries, material properties, process considerations, and reliability testing for polymers used in wafer level packaging including epoxy mold compounds and dielectric redistribution layers (RDL) for eWLP. The course has been completely updated to include a detailed discussion of the polymers and polymer-related processing for Fan-Out Wafer Level packaging such as chip first and chip last (RDL first).

# **Course Outline:**

- 1. Overview of Polymers Used in Wafer Level Packaging

- 2. Wafer Level Process Flows (Chip First Versus Chip Last (RDL First))

- 3. Epoxy Mold Compounds for eWLP

- Photosensitive Polyimides and 4. Polybenzoxazoles

- 5. Pre-Applied Underfills and Wafer Level Underfills, Chemistry and Process

- Polymer Challenges in Fan-Out Wafer Level 6 Packaging

- 7. Reliability Testing for Fan-Out Wafer Level

- Packaging 8. Wafer Versus Panel Processing, Polymer Challenges and Solutions

- Polymers Used in Heterogeneous Integration 9 Fanout Panel Level Packaging (FO-PLP)

#### Who Should Attend:

Packaging engineers involved in the development. production, and reliability testing of semiconductor packages would benefit from the course. R&D professionals interested in gaining a basic understanding of the structure/property/ process/performance relationships in polymers and polymer-based materials used in electronic packaging will also find this course valuable.

#### **15. RELIABILITY MECHANICS AND MODELING FOR IC PACKAGING** Course Leaders: Ricky Lee - HKUST and Xuejun Fan – Lamar University

#### **Course Objective:**

This course aims to present a comprehensive coverage of reliability mechanics and modeling under various loading conditions. In addition to the introduction of fundamentals, the course contents are arranged in four modules. Module 1 covers modeling under thermal loading, such as problems related to mismatch of thermal expansion or non-uniform temperature distribution. Module 2 deals with the modeling under mechanical loading, such as mechanical bending and/or drop impact. Module 3 will cover modeling under humidity/moisture loading for moisture related problems, such as failures in soldering reflow as well as under HAST and biHAST. Module 4 will introduce multi-physics modeling that involves the combined thermal, moisture, electrical, and mechanical loading. Theoretical foundation, modeling implementation, and the best practices for numerical simulations will be covered. Emerging trend and future perspective in reliability mechanics and modeling will be discussed.

#### **Course Outline:**

- Fundamentals of Stress Analysis and 1. Computational Modeling for IC Packaging

- 2. Reliability Issues and Modeling Under Thermal Loading

- 3. Reliability Issues and Modeling Under Mechanical Loading

- 4. Reliability Issues and Modeling Under Moisture/Humidity Loading

- Reliability Issues and Modeling Under Combined Loading - Multi-Physics Modeling

#### Who Should Attend?

This course is intended for technical managers and staff members, reliability engineers, scientific researchers, and graduate students who are involved in thermal/mechanical modeling, package design, material selection, qualification and reliability assessment of chip-package interaction, package, and package/board interaction.

### **IMPORTANT NOTICE**

It is extremely important to register in advance to prevent delays at door registration. Course sizes are limited.

#### **16. POWER ELECTRONICS FOR AUTOMOTIVE APPLICATIONS** Course Leader: Mervi Paulasto-Kröckel -**Aalto University**

### **Course Objective:**

The amount of electronics in vehicles has increased dramatically over the last several years and will continue to increase further in the future. Power electronics plays a major role in controlling automotive electronics and with the transition to energy-efficient forms of mobility its importance is even greater. E-mobility also strongly increases power-levels of related converters, such as HEV/EV main inverters and other high-voltage systems requiring new type of high-power module packages. The new package concepts and technologies have to be qualified to meet the reliability and automotive standards safety while simultaneously increasing life time requirements. This course provides an overview of what kind of power technologies, packaging concepts and materials are currently being used in different products from power semiconductors to power modules. What are the prevailing trends and challenges that power electronic packaging engineers face in automotive applications? This course will start by reviewing application areas for different power semiconductor technologies. Then different power packages and interconnect technologies used in these automotive applications will be introduced. Power module packaging concepts will be explained, and the requirements and possible concepts for e-mobility will be presented. The lecture will then proceed to reliability issues of the power packages and modules. In this context, robustness validation and design for reliability is covered. Finally, new developments in terms of materials and their implications on performance, thermal management, and reliability will be discussed.

#### **Course Outline:**

- 1. Power Electronics for Automotive What and Where?

- 2. Background Power Semiconductors and Power Conversion

- 3. Power Electronics Packaging

- Requirements and Challenges

- Interconnects for Power Devices: Die Attach and Pb-Rich Solder Interconnects: and, Wire Bonding and Low RDSon Interconnects

- Thermal Management in Power Packaging

- Chip Embedding in Laminate Packaging

- Power Modules structure and Interconnects

- WBG Semiconductors What is Changing?

- 4. Typical Failure Mechanisms in Power Packages

- Robustness Validation and Design for 5